- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24814 > 935265435112 (NXP SEMICONDUCTORS) 8-BIT, FLASH, 33 MHz, MICROCONTROLLER, PQCC44 PDF資料下載

參數(shù)資料

| 型號(hào): | 935265435112 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, FLASH, 33 MHz, MICROCONTROLLER, PQCC44 |

| 封裝: | PLASTIC, MO-047, SOT-187-2, LCC-44 |

| 文件頁數(shù): | 28/52頁 |

| 文件大?。?/td> | 288K |

| 代理商: | 935265435112 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當(dāng)前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

Philips Semiconductors

Preliminary data

P89C51RB2/P89C51RC2/

P89C51RD2

80C51 8-bit Flash microcontroller family

16KB/32KB/64KB ISP/IAP Flash with 512B/512B/1KB RAM

2001 Jun 27

34

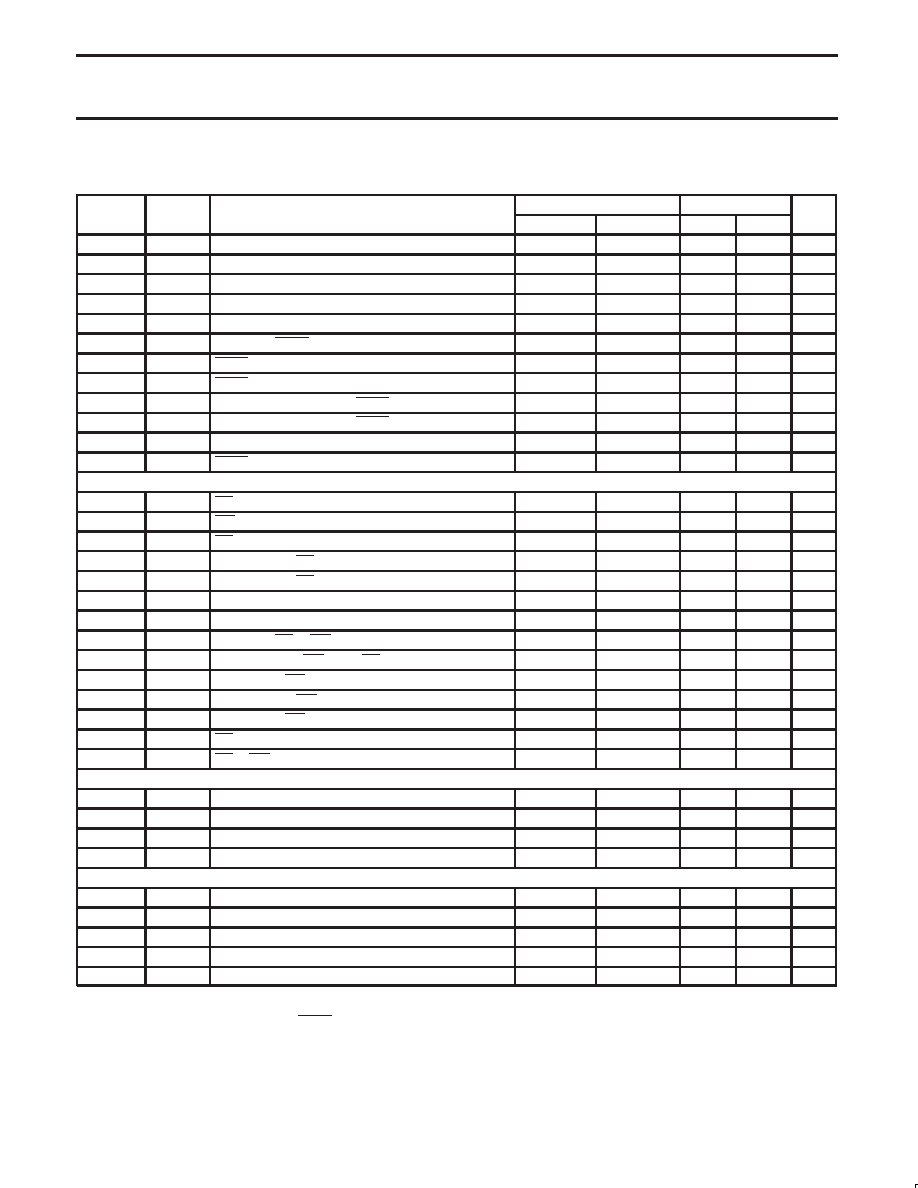

AC ELECTRICAL CHARACTERISTICS (12 CLOCK MODE)

Tamb = 0°C to +70°C; VCC = 5 V ± 10% or –40°C to +85°C, VCC = 5 V ±5%, VSS = 0 V1, 2, 3

VARIABLE CLOCK4

33 MHz CLOCK4

SYMBOL

FIGURE

PARAMETER

MIN

MAX

MIN

MAX

UNIT

1/tCLCL

29

Oscillator frequency

0

33

0

33

MHz

tLHLL

29

ALE pulse width

2tCLCL–40

21

ns

tAVLL

29

Address valid to ALE low

tCLCL–25

5

ns

tLLAX

29

Address hold after ALE low

tCLCL–25

5

ns

tLLIV

29

ALE low to valid instruction in

4tCLCL–65

55

ns

tLLPL

29

ALE low to PSEN low

tCLCL–25

5

ns

tPLPH

29

PSEN pulse width

3tCLCL–45

45

ns

tPLIV

29

PSEN low to valid instruction in

3tCLCL–60

30

ns

tPXIX

29

Input instruction hold after PSEN

0

ns

tPXIZ

29

Input instruction float after PSEN

tCLCL–25

5

ns

tAVIV

29

Address to valid instruction in

5tCLCL–80

70

ns

tPLAZ

29

PSEN low to address float

10

ns

Data Memory

tRLRH

30, 31

RD pulse width

6tCLCL–100

82

ns

tWLWH

30, 31

WR pulse width

6tCLCL–100

82

ns

tRLDV

30, 31

RD low to valid data in

5tCLCL–90

60

ns

tRHDX

30, 31

Data hold after RD

0

ns

tRHDZ

30, 31

Data float after RD

2tCLCL–28

32

ns

tLLDV

30, 31

ALE low to valid data in

8tCLCL–150

90

ns

tAVDV

30, 31

Address to valid data in

9tCLCL–165

105

ns

tLLWL

30, 31

ALE low to RD or WR low

3tCLCL–50

3tCLCL+50

40

140

ns

tAVWL

30, 31

Address valid to WR low or RD low

4tCLCL–75

45

ns

tQVWX

30, 31

Data valid to WR transition

tCLCL–30

0

ns

tWHQX

30, 31

Data hold after WR

tCLCL–25

5

ns

tQVWH

31

Data valid to WR high

7tCLCL–130

80

ns

tRLAZ

30, 31

RD low to address float

0

ns

tWHLH

30, 31

RD or WR high to ALE high

tCLCL–25

tCLCL+25

5

55

ns

External Clock

tCHCX

33

High time

17

tCLCL–tCLCX

ns

tCLCX

33

Low time

17

tCLCL–tCHCX

ns

tCLCH

33

Rise time

5

ns

tCHCL

33

Fall time

5

ns

Shift Register

tXLXL

32

Serial port clock cycle time

12tCLCL

360

ns

tQVXH

32

Output data setup to clock rising edge

10tCLCL–133

167

ns

tXHQX

32

Output data hold after clock rising edge

2tCLCL–80

50

ns

tXHDX

32

Input data hold after clock rising edge

0

ns

tXHDV

32

Clock rising edge to input data valid

10tCLCL–133

167

ns

NOTES:

1. Parameters are valid over operating temperature range unless otherwise specified.

2. Load capacitance for port 0, ALE, and PSEN = 100 pF, load capacitance for all other outputs = 80 pF.

3. Interfacing the microcontroller to devices with float times up to 45 ns is permitted. This limited bus contention will not cause damage to

Port 0 drivers.

4. Parts are tested to 3.5 MHz, but guaranteed to operate down to 0 Hz.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935267813557 | 8-BIT, FLASH, 33 MHz, MICROCONTROLLER, PQFP44 |

| 08-50-0031 | 2.5mm KK Crp Term Chn il W/Ct Ear |

| 08-50-0032 | CRIMP PIN, 22-30AWG, PK1000; Series:KK; Connector type:Contact, Crimp; Gender:Socket; Termination method:Crimp; Material, contact:Brass; Plating, contact:Tin; Wire size, AWG:22AWG; Approval Bodies:UL, CSA; Area, wire size RoHS Compliant: Yes |

| 08-50-0030 | 2.5mm KK Crp Term Chn il W/Ct Ear 2.2mm |

| 08-55-0112 | 2.5mm KK Crp Term Chn il W/Ct Ear 2.2mm |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

| 935269544557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-2US1-V1.3 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。