- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24813 > 935264164112 (NXP SEMICONDUCTORS) LVT SERIES, 16 1-BIT DRIVER, TRUE OUTPUT, PDSO48 PDF資料下載

參數(shù)資料

| 型號(hào): | 935264164112 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 總線收發(fā)器 |

| 英文描述: | LVT SERIES, 16 1-BIT DRIVER, TRUE OUTPUT, PDSO48 |

| 封裝: | 6.10 MM, PLASTIC, MO-153ED, SOT-362-1, TSSOP-48 |

| 文件頁(yè)數(shù): | 5/12頁(yè) |

| 文件大小: | 121K |

| 代理商: | 935264164112 |

Philips Semiconductors

Product specification

74LVT162373

3.3 V LVT 16-bit transparent D-type latch

with 30

termination resistors (3-State)

2

1999 Sep 23

853-2172 22406

FEATURES

16-bit transparent latch

3-State buffers

Output capability: +12 mA / –12 mA

TTL input and output switching levels

Input and output interface capability to systems at 5 V supply

Bus-hold data inputs eliminate the need for external pull-up

resistors to hold unused inputs

Live insertion/extraction permitted

Outputs include series resistance of 30 making external

resistors unnecessary

Power-up reset

Power-up 3-State

No bus current loading when output is tied to 5 V bus

Latch-up protection exceeds 500 mA per JEDEC Std 17

ESD protection exceeds 2000 V per MIL STD 883 Method 3015

and 200 V per Machine Model

DESCRIPTION

The 74LVT162373 is a high-performance BiCMOS product designed

for VCC operation at 3.3 V.

This device is a 16-bit transparent D-type latch with non-inverting

3-State bus compatible outputs. The device can be used as two

8-bit latches or one 16-bit latch. When Latch Enable (LE) input is

High, the Q outputs follow the data (D) inputs. When Latch Enable is

taken Low, the Q outputs are latched at the levels of the D inputs

one setup time prior to the High-to-Low transition.

The 74LVT162373 is designed with 30

series resistance in both

the High and Low states of the output. This design reduces the

noise in applications such as memory address drivers, clock drivers,

and bus receivers/transmitters.

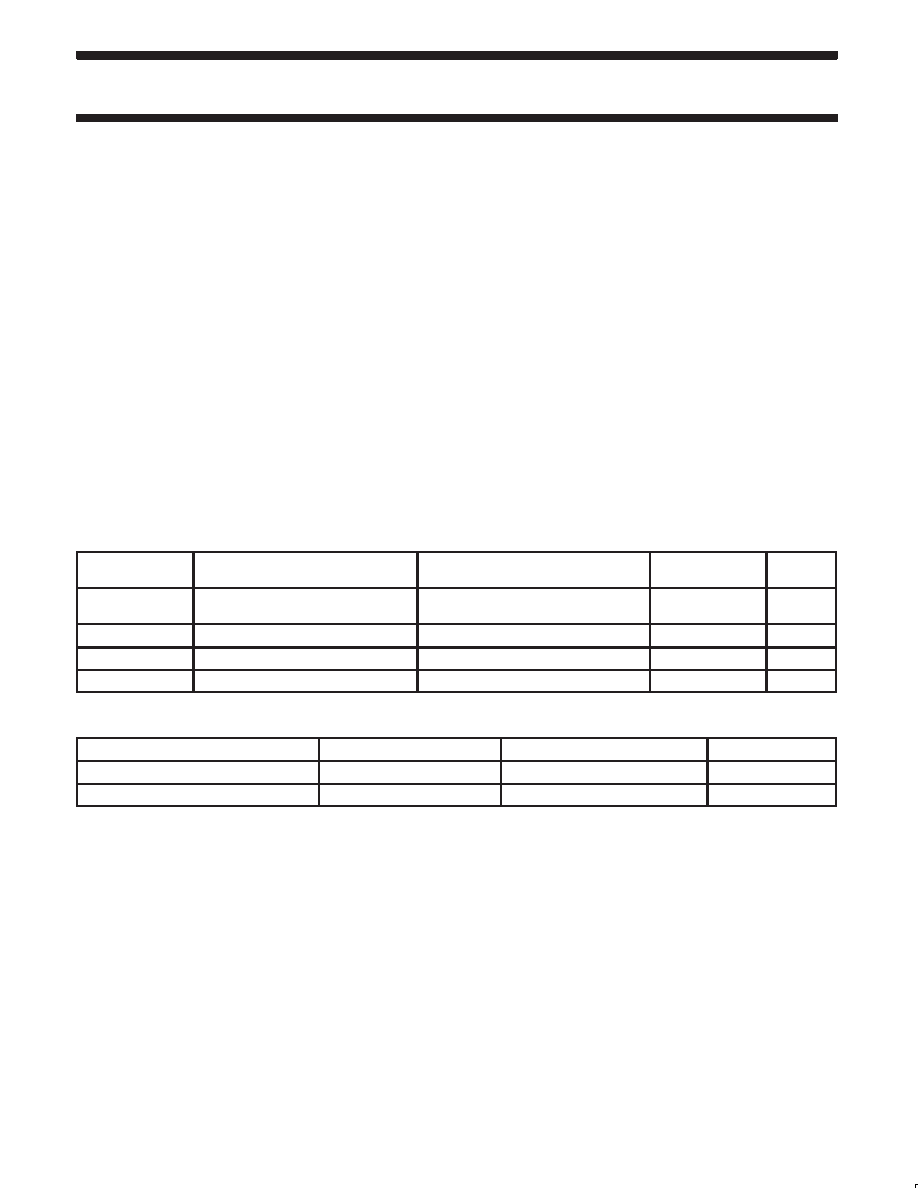

QUICK REFERENCE DATA

SYMBOL

PARAMETER

CONDITIONS

Tamb = 25 °C

TYPICAL

UNIT

tPLH

tPHL

Propagation delay

nDx to nQx

CL = 50 pF;

VCC = 3.3 V

3.0

ns

CIN

Input capacitance

VI = 0 V or 3.0 V

3

pF

COUT

Output capacitance

Outputs disabled; VO = 0 V or 3.0 V

9

pF

ICCZ

Total supply current

Outputs disabled; VCC = 3.6 V

70

A

ORDERING INFORMATION

PACKAGES

TEMPERATURE RANGE

ORDERING CODE

DWG NUMBER

48-Pin Plastic SSOP Type III

–40

°C to +85 °C

74LVT162373 DL

SOT370-1

48-Pin Plastic TSSOP Type II

–40

°C to +85 °C

74LVT162373 DGG

SOT362-1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935264163118 | LVT SERIES, 16 1-BIT DRIVER, TRUE OUTPUT, PDSO48 |

| 935264167112 | LVT SERIES, 16 1-BIT DRIVER, TRUE OUTPUT, PDSO48 |

| 935264166112 | LVT SERIES, 16 1-BIT DRIVER, TRUE OUTPUT, PDSO48 |

| 935264166118 | LVT SERIES, 16 1-BIT DRIVER, TRUE OUTPUT, PDSO48 |

| 935264184112 | AHCT/VHCT SERIES, 8-INPUT NAND GATE, PDSO14 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。