- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24676 > 935263181026 (NXP SEMICONDUCTORS) LIQUID CRYSTAL DISPLAY DRIVER, UUC56 PDF資料下載

參數(shù)資料

| 型號: | 935263181026 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 顯示驅(qū)動器 |

| 英文描述: | LIQUID CRYSTAL DISPLAY DRIVER, UUC56 |

| 封裝: | DIE |

| 文件頁數(shù): | 42/43頁 |

| 文件大小: | 327K |

| 代理商: | 935263181026 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁當(dāng)前第42頁第43頁

1997 Apr 01

8

Philips Semiconductors

Product specication

LCD column driver for dot matrix graphic

displays

PCF8579

7

FUNCTIONAL DESCRIPTION

The PCF8579 column driver is designed for use with the

PCF8578. Together they form a general purpose LCD dot

matrix chip set.

Typically up to 16 PCF8579s may be used with one

PCF8578. Each of the PCF8579s is identified by a unique

4-bit hardware subaddress, set by pins A0 to A3.

The PCF8578 can operate with up to 32 PCF8579s when

using two I2C-bus slave addresses. The two slave

addresses are set by the logic level on input SA0.

7.1

Multiplexed LCD bias generation

The bias levels required to produce maximum contrast

depend on the multiplex rate and the LCD threshold

voltage (Vth). Vth is typically defined as the RMS voltage at

which the LCD exhibits 10% contrast. Table 1 shows the

optimum voltage bias levels for the PCF8578/PCF8579

chip set as functions of Vop (Vop =VDD VLCD), together

with the discrimination ratios (D) for the different multiplex

rates. A practical value for Vop is obtained by equating

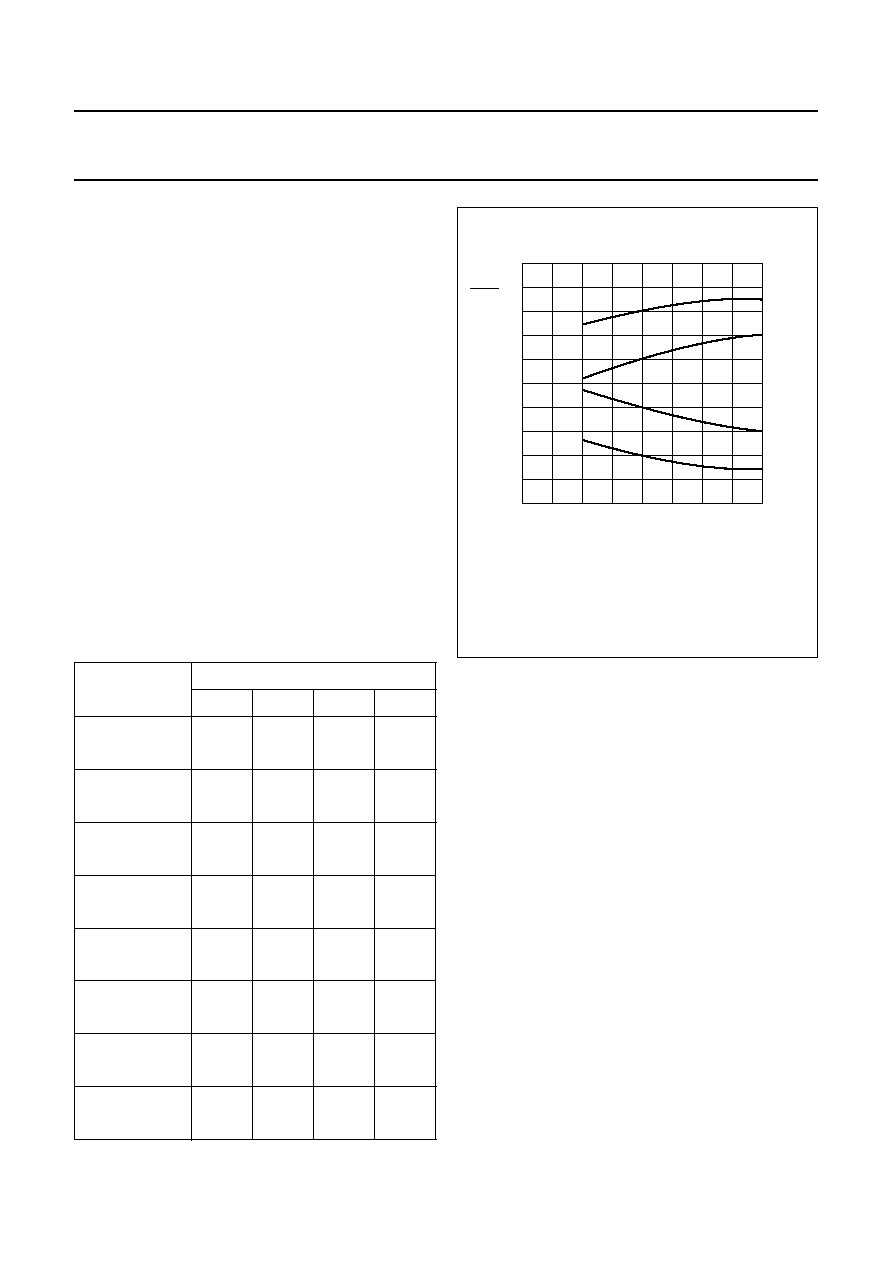

Voff(rms) with Vth. Figure 4 shows the first 4 rows of Table 1

as graphs.

Table 1 Optimum LCD bias voltages

PARAMETER

MULTIPLEX RATE

1:8

1:16

1:24

1:32

0.739

0.800

0.830

0.850

0.522

0.600

0.661

0.700

0.478

0.400

0.339

0.300

0.261

0.200

0.170

0.150

0.297

0.245

0.214

0.193

0.430

0.316

0.263

0.230

1.447

1.291

1.230

1.196

3.370

4.080

4.680

5.190

V

2

V

op

---------

V

3

V

op

---------

V

4

V

op

---------

V

5

V

op

---------

V

off rms

()

V

op

-----------------------

V

on rms

()

V

op

-----------------------

D

V

on rms

()

V

off rms

()

-----------------------

=

V

op

V

th

---------

7.2

Power-on reset

At power-on the PCF8579 resets to a defined starting

condition as follows:

1. Display blank (in conjunction with PCF8578)

2. 1 : 32 multiplex rate

3. Start bank, 0 selected

4. Data pointer is set to X, Y address 0, 0

5. Character mode

6. Subaddress counter is set to 0

7. I2C-bus is initialized.

Data transfers on the I2C-bus should be avoided for 1 ms

following power-on, to allow completion of the reset action.

Fig.4

Vbias/Vop as a function of the multiplex rate.

1:8

1:16

1:32

1.0

0

0.8

MSA838

1:24

0.6

0.4

0.2

multiplex rate

V bias

Vop

V5

V4

V3

V2

Vbias =V2, V3, V4, V5. See Table 1.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935263316026 | LIQUID CRYSTAL DISPLAY DRIVER, UUC56 |

| 933964690623 | F/FAST SERIES, 8-BIT RIGHT SERIAL IN PARALLEL OUT SHIFT REGISTER, TRUE OUTPUT, PDSO16 |

| 0570360000 | 24 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| 933966340235 | 300 mA, 60 V, N-CHANNEL, Si, SMALL SIGNAL, MOSFET, TO-236AB |

| 933966340215 | 300 mA, 60 V, N-CHANNEL, Si, SMALL SIGNAL, MOSFET, TO-236AB |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。