- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄208948 > 8741004AGLF (INTEGRATED DEVICE TECHNOLOGY INC) 8741004 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO24 PDF資料下載

參數(shù)資料

| 型號(hào): | 8741004AGLF |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時(shí)鐘及定時(shí) |

| 英文描述: | 8741004 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO24 |

| 封裝: | 4 40 X 7.80 MM, 0.92 MM HEIGHT, ROHS COMPLIANT, MO-153, TSSOP-24 |

| 文件頁(yè)數(shù): | 13/19頁(yè) |

| 文件大小: | 784K |

| 代理商: | 8741004AGLF |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)

ICS8741004

DIFFERENTIAL-TO-LVDS/0.7V DIFFERENTIAL PCI EXPRESS JITTER ATTENUATOR

IDT / ICS PCI EXPRESS JITTER ATTENUATOR

3

ICS8741004AG REV. AMAY 29, 2008

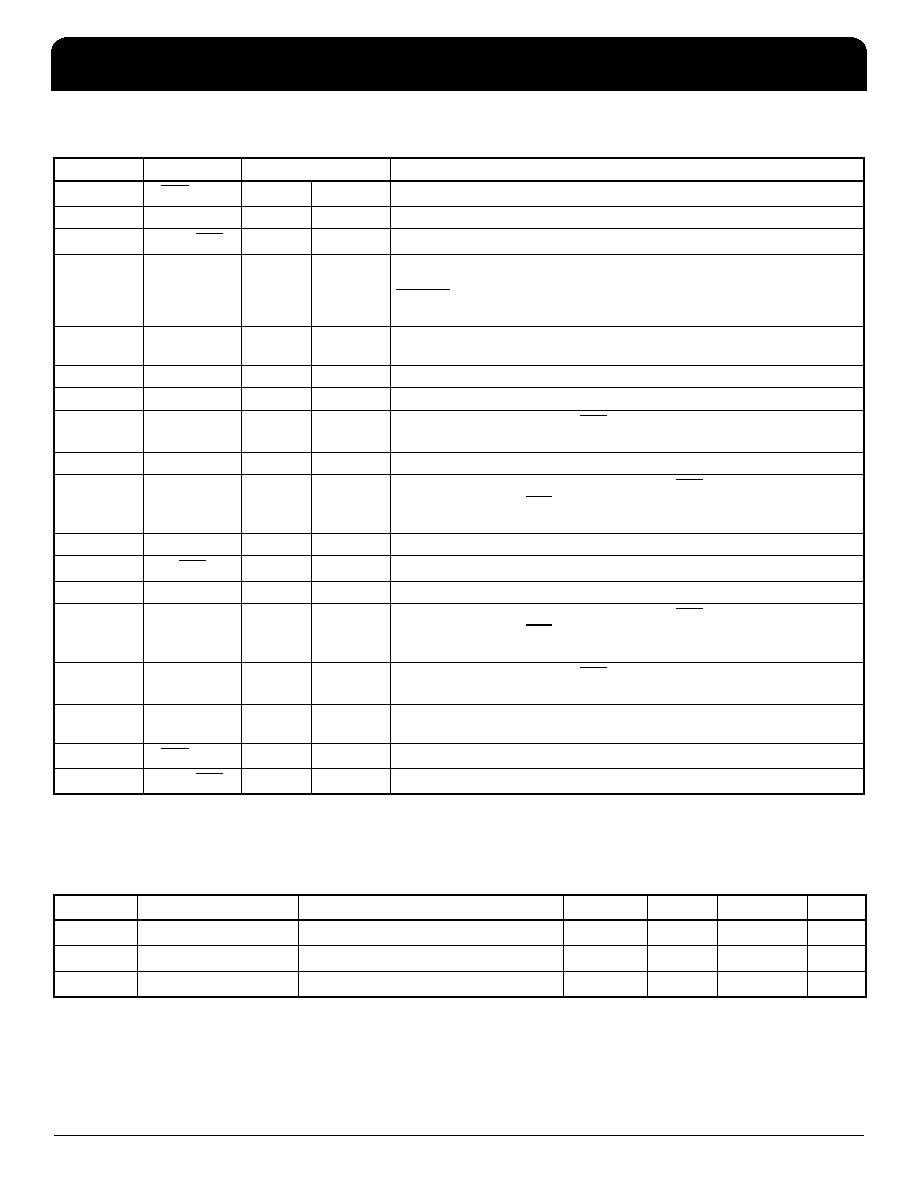

Table 1. Pin Descriptions

NOTE: Pullup and Pulldown refer to internal input resistors. See Table 2, Pin Characteristics, for typical values.

Table 2. Pin Characteristics

Number

Name

Type

Description

1, 2

QA1, QA1

Output

Differential output pair. LVDS interface levels.

3, 22

VDDO

Power

Output supply pins.

4, 5

QA0, QA0

Output

Differential output pair. LVDS interface levels.

6

MR

Input

Pulldown

Active High Master Reset. When logic HIGH, the internal dividers are reset

causing the true outputs Q[Ax:Bx] to go LOW and the inverted outputs

Q[Ax:Bx] to go HIGH. When logic LOW, the internal dividers and the outputs

are enabled. LVCMOS/LVTTL interface levels.

7

BW_SEL

Input

Pullup/

Pulldown

PLL Bandwidth input. LVCMOS/LVTTL interface levels. See Table 3B.

8

nc

Unused

No connect.

9VDDA

Power

Analog supply pin.

10

F_SELA

Input

Pulldown

Frequency select pins for QAx/QAx outputs.

LVCMOS/LVTTL interface levels. See Table 3C.

11

VDD

Power

Core supply pin.

12

OEA

Input

Pullup

Output enable for QAx pins. When HIGH, QAx/QAx outputs are enabled.

When LOW, the QAx/QAx outputs are in a high impedance state.

LVCMOS/LVTTL interface levels. See Table 3A.

13

CLK

Input

Pulldown

Non-inverting differential clock input.

14

CLK

Input

Pullup

Inverting differential clock input.

15, 16

GND

Power

Power supply ground.

17

OEB

Input

Pullup

Output enable for QBx pins. When HIGH, QBx/QBx outputs are enabled.

When LOW, the QBx/QBx outputs are in a high impedance state.

LVCMOS/LVTTL interface levels. See Table 3A.

18

F_SELB

Input

Pulldown

Frequency select pins for QBx/QBx outputs.

LVCMOS/LVTTL interface levels. See Table 3C.

19

IREF

Input

A fixed precision resistor (RREF = 475

) from this pin to ground provides a

reference current used for differential current-mode QB0/nQB0 clock outputs.

20, 21

QB0, QB0

Output

Differential output pair. HCSL interface levels.

23, 24

QB1, QB1

Output

Differential output pair. HCSL interface levels.

Symbol

Parameter

Test Conditions

Minimum

Typical

Maximum

Units

CIN

Input Capacitance

4

pF

RPULLUP

Input Pullup Resistor

51

k

RPULLDOWN Input Pulldown Resistor

51

k

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 800-033-BDHL8ZNU6-7PX-72 | INTERCONNECTION DEVICE |

| 800-033-CAKL2ZNU6-7NX-72 | INTERCONNECTION DEVICE |

| 800-033-CAKL2ZNU7-10NY-72 | INTERCONNECTION DEVICE |

| 800-033-CAKL4NF6-7NZ-72 | INTERCONNECTION DEVICE |

| 800-033-BDKL4M6-4PZ-72 | INTERCONNECTION DEVICE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 8741004AGLFT | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 LVDS/HCSL PCIe Jitter Attenuator RoHS:否 制造商:IDT 輸出端數(shù)量:2 輸出電平:LVCMOS, LVDS, LVPECL 最大輸出頻率:250 MHz 輸入電平:HCSL, LVDS, LVHSTL, LVPECL 最大輸入頻率:710 MHz 電源電壓-最大:3.465 V 電源電壓-最小:3.135 V 封裝 / 箱體:VFQFN-40 封裝: |

| 8741004AGT | 制造商:Integrated Device Technology Inc 功能描述:PLL FREQ SYNTHESIZER SGL 24TSSOP - Tape and Reel |

| 8741004BGI | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:DIFFERENTIAL-TO-LVDS/0.7V DIFFERENTIAL PCI EXPRESS⑩ JITTER ATTENUATOR |

| 8741004BGILF | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 8741004BGILFT | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。