- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄294557 > 873995AY (INTEGRATED DEVICE TECHNOLOGY INC) 873995 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 PDF資料下載

參數(shù)資料

| 型號: | 873995AY |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 873995 SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP48 |

| 封裝: | 7 X 7 MM, 1 MM HEIGHT, MS-026, TQFP-48 |

| 文件頁數(shù): | 5/20頁 |

| 文件大?。?/td> | 332K |

| 代理商: | 873995AY |

IDT / ICS LVPECL ZERO DELAY/MULTIPLIER/DIVIDER

13

ICS873995AY REV. A SEPTEMBER 11, 2008

ICS873995

DIFFERENTIAL-TO-3.3V LVPECL ZERO DELAY/MULTIPLIER/DIVIDER

EPAD THERMAL RELEASE PATH

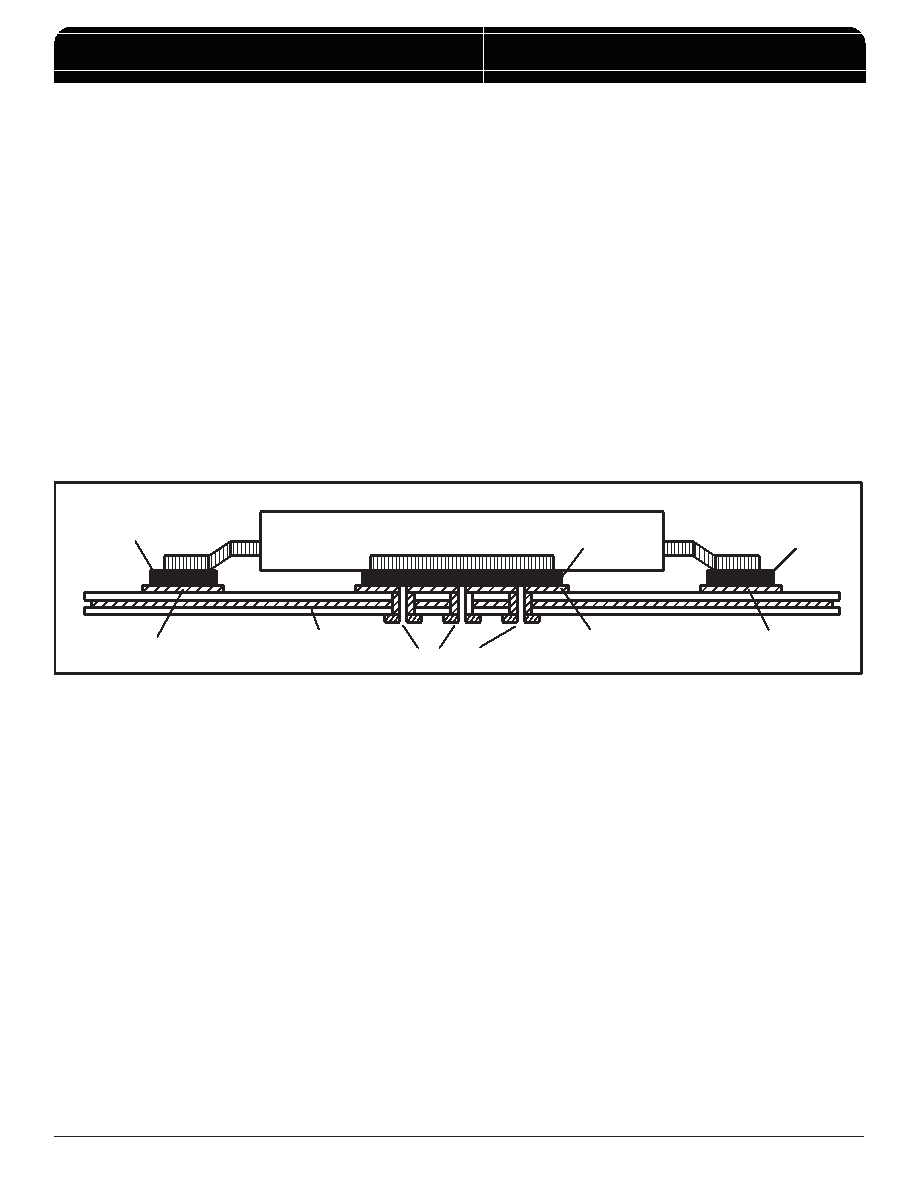

In order to maximize both the removal of heat from the package

and the electr ical perfor mance, a land patter n must be

incorporated on the Printed Circuit Board (PCB) within the footprint

of the package corresponding to the exposed metal pad or

exposed heat slug on the package, as shown in

Figure 5. The

solderable area on the PCB, as defined by the solder mask, should

be at least the same size/shape as the exposed pad/slug area on

the package to maximize the thermal/electrical performance.

Sufficient clearance should be designed on the PCB between the

outer edges of the land pattern and the inner edges of pad pattern

for the leads to avoid any shorts.

While the land pattern on the PCB provides a means of heat

transfer and electrical grounding from the package to the board

through a solder joint, thermal vias are necessary to effectively

conduct from the surface of the PCB to the ground plane(s). The

land pattern must be connected to ground through these vias.

The vias act as “heat pipes”. The number of vias (i.e. “heat pipes”)

are application specific and dependent upon the package power

dissipation as well as electrical conductivity requirements. Thus,

thermal and electrical analysis and/or testing are recommended

to determine the minimum number needed. Maximum thermal

and electrical performance is achieved when an array of vias is

incorporated in the land pattern. It is recommended to use as

many vias connected to ground as possible. It is also

recommended that the via diameter should be 12 to 13mils (0.30

to 0.33mm) with 1oz copper via barrel plating. This is desirable to

avoid any solder wicking inside the via during the soldering process

which may result in voids in solder between the exposed pad/

slug and the thermal land. Precautions should be taken to

eliminate any solder voids between the exposed heat slug and

the land pattern. Note: These recommendations are to be used

as a guideline only. For further information, refer to the Application

Note on the

Surface Mount Assembly of Amkor’s Thermally/

Electrically Enhance Leadfame Base Package, Amkor Technology.

GROUND PLANE

LAND PATTERN

SOLDER

THERMAL VIA

EXPOSED HEAT SLUG

(GROUND PAD)

PIN

PIN PAD

SOLDER

PIN

PIN PAD

SOLDER

FIGURE 5. P.C. BOARD FOR EXPOSED PAD THERMAL RELEASE PATH EXAMPLE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 874-11-3 | PANEL MOUNT, CABLE TERMINATED, SMA CONNECTOR, SOLDER, RECEPTACLE |

| 874003DG-02T | 874003 SERIES, PLL BASED CLOCK DRIVER, 3 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

| 875-100-3 | CABLE TERMINATED, MALE, SMA CONNECTOR, CRIMP, PLUG |

| 87533-1010 | 160 CONTACT(S), FEMALE, STRAIGHT SINGLE PART CARD EDGE CONN, SURFACE MOUNT, SOCKET |

| 87533-1020 | 160 CONTACT(S), FEMALE, STRAIGHT SINGLE PART CARD EDGE CONN, SURFACE MOUNT, SOCKET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 873995AYLF | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-56 |

| 873995AYLFT | 制造商:Integrated Device Technology Inc 功能描述:Zero Delay PLL Clock Multiplier Single 48-Pin TQFP EP T/R 制造商:Integrated Device Technology Inc 功能描述:ZERO DLY PLL CLOCK MLTPLR SGL 48TQFP EP - Tape and Reel |

| 873995AYT | 制造商:Integrated Device Technology Inc 功能描述:873995AYT - Tape and Reel |

| 873996AY | 制造商:Integrated Device Technology Inc 功能描述:Zero Delay PLL Clock Multiplier Single 48-Pin TQFP EP Tray 制造商:Integrated Device Technology Inc 功能描述:873996AY - Trays |

| 873996AYLF | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-56 |

發(fā)布緊急采購,3分鐘左右您將得到回復。