- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360547 > 7LVC623APWDH (NXP SEMICONDUCTORS) Octal transceiver with dual enable 3-State PDF資料下載

參數(shù)資料

| 型號: | 7LVC623APWDH |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 通用總線功能 |

| 英文描述: | Octal transceiver with dual enable 3-State |

| 中文描述: | LVC/LCX/Z SERIES, 8-BIT TRANSCEIVER, TRUE OUTPUT, PDSO20 |

| 文件頁數(shù): | 2/10頁 |

| 文件大?。?/td> | 96K |

| 代理商: | 7LVC623APWDH |

Philips Semiconductors

Product specification

74LVC623A

Octal transceiver with dual enable (3-State)

2

1998 Jul 29

853-2106 19803

FEATURES

Wide supply voltage range of 1.2V to 3.6V

In accordance with JEDEC standard no. 8-1A

Flow-through pin-out architecture

CMOS low power consumption

Inputs accept voltages up to 5.5V

Direct interface with TTL levels

Output drive capability 50 transmission lines @ 85

°

C

DESCRIPTION

The 74LVC623A is a high performance, low-power, low-voltage

Si-gate CMOS device, superior to most advanced CMOS

compatible TTL families.

The 74LVC623A is an octal transceiver featuring non-inverting

3-State bus compatible outputs in both send and receive directions.

This octal bus transceiver is designed for asynchronous two-way

communication between data buses.

The control function implementation allows maximum flexibility in

timing. This device allows data transmission from the A bus to the B

bus or from the B bus to the A bus, depending upon the levels at the

enable inputs (OEAB, OEBA). The enable inputs can be used to

disable the device so that the buses are effectively isolated. The

dual enable function configuration gives this transceiver the

capability to store data by simultaneous enabling of OEAB and

OEBA. Each output reinforces its input in this transceiver

configuration. Thus, when both control inputs are enabled and all

other data sources to the two sets of the bus lines are at high

impedance OFF-state, both sets of bus lines will remain at their last

states. The 8-bit codes appearing on the two sets of buses will be

identical.

The ‘623A’ is identical to the ‘620A’ but has true (non-inverting)

outputs.

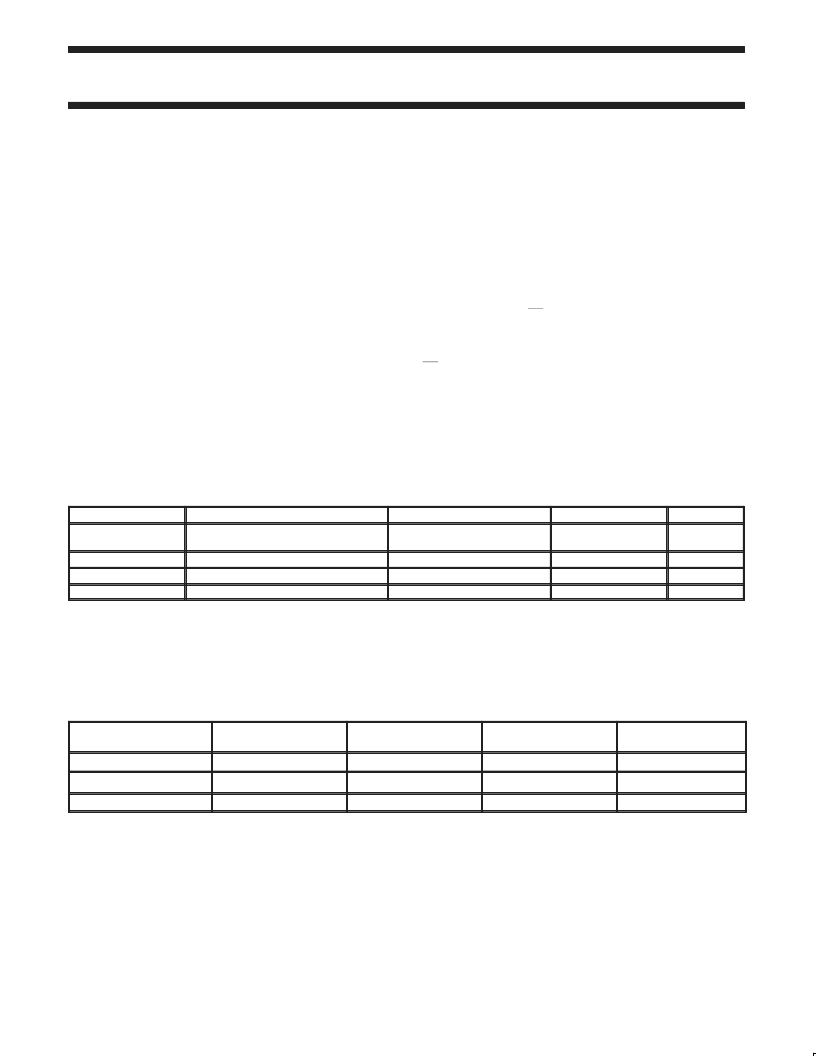

QUICK REFERENCE DATA

GND = 0V; T

amb

= 25

°

C; t

r

= t

f

SYMBOL

2.5 ns

PARAMETER

CONDITIONS

TYPICAL

UNIT

t

PHL

/t

PLH

Propagation delay

An to Bn; Bn to An

Input capacitance

Input/output capacitance

Power dissipation capacitance per latch

C

L

= 50pF

V

CC

= 3.3V

3.3

5.0

10

32

ns

C

I

C

I/O

C

PD

NOTES:

1. C

PD

is used to determine the dynamic power dissipation (P

D

in

μ

W)

P

D

= C

PD

V

CC2

x f

i

Σ

(C

L

f

i

= input frequency in MHz; C

L

= output load capacity in pF;

f

o

= output frequency in MHz; V

CC

= supply voltage in V;

Σ

(C

L

V

CC2

f

o

) = sum of the outputs.

2. The condition is V

I

= GND to V

CC.

pF

pF

pF

Notes 1, 2

V

CC2

f

o

) where:

ORDERING AND PACKAGE INFORMATION

PACKAGES

TEMPERATURE RANGE

OUTSIDE NORTH

AMERICA

NORTH AMERICA

PKG. DWG. #

20-Pin Plastic SO

–40

°

C to +85

°

C

74LVC623A D

74LVC623A D

SOT163-1

20-Pin Plastic SSOP Type II

–40

°

C to +85

°

C

–40

°

C to +85

°

C

74LVC623A DB

74LVC623A DB

SOT339-1

20-Pin Plastic TSSOP Type I

74LVC623A PW

7LVC623APW DH

SOT360-1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 7LVC646APWDH | Octal bus transceiver/register 3-State |

| 7LVC827APWDH | 10-bit buffer/line driver with 5-volt tolerant inputs/outputs 3-State |

| 7LVC841APWDH | 10-bit transparent latch with 5-volt tolerant inputs/outputs 3-State |

| 7LVT2241PWDH | 3.3V Octal buffer/line driver with 30ohm series termination resistors; 3-State |

| 7LVT2244PWDH | 3.3V Octal buffer/line driver with 30ohm series termination resistors 3-State |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 7LVC646APWDH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Octal bus transceiver/register 3-State |

| 7LVC827APWDH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:10-bit buffer/line driver with 5-volt tolerant inputs/outputs 3-State |

| 7LVC841APWDH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:10-bit transparent latch with 5-volt tolerant inputs/outputs 3-State |

| 7LVT2241PWDH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:3.3V Octal buffer/line driver with 30ohm series termination resistors; 3-State |

| 7LVT2244PWDH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:3.3V Octal buffer/line driver with 30ohm series termination resistors 3-State |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。