- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382827 > 79RC64575 (Integrated Device Technology, Inc.) Advanced 64-bit Microprocessors Product Family PDF資料下載

參數(shù)資料

| 型號: | 79RC64575 |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | Advanced 64-bit Microprocessors Product Family |

| 中文描述: | 高級的64位微處理器產(chǎn)品系列 |

| 文件頁數(shù): | 8/28頁 |

| 文件大小: | 399K |

| 代理商: | 79RC64575 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

8 of 28

December 14, 2001

79RC64574 79RC64575

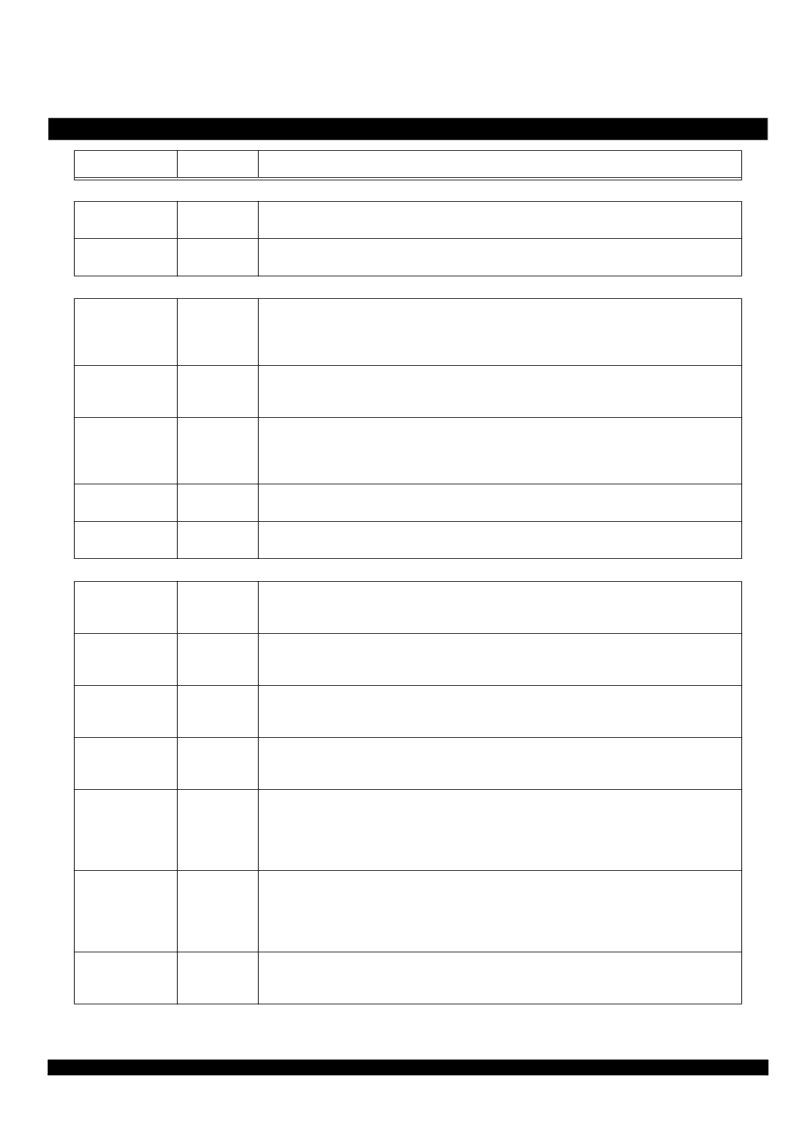

Interrupt Interface

Int*(5:0)

I

Interrupt

Six general processor interrupts, bit-wise ORed with bits 5:0 of the interrupt register.

NMI*

I

Non-maskable interrupt

Non-maskable interrupt, ORed with bit 6 of the interrupt register.

Initialization Interface

V

CC

O

k

I

V

CC

is OK

When asserted, this signal indicates to the processor that the power supply has been above the Vcc minimum

for more than 100 milliseconds and will remain stable. The assertion of V

CCO

k initiates the initialization

sequence.

ColdReset*

I

Cold reset

This signal must be asserted for a power on reset or a cold reset. ColdReset must be de-asserted synchro-

nously with SysClock.

Reset*

I

Reset

This signal must be asserted for any reset sequence. It can be asserted synchronously or asynchronously for

a cold reset, or synchronously to initiate a warm reset. Reset must be de-asserted synchronously with

SysClock.

ModeClock

O

Boot-mode clock

Serial boot-mode data clock output at the system clock frequency divided by two hundred fifty-six.

ModeIn

I

Boot-mode data in

Serial boot-mode data input.

JTAG Interface

TDI

I

JTAG Data In

On the rising edge of TCK, serial input data are shifted into either the Instruction register or Data register,

depending on the TAP controller state. An external pull-up resistor is required.

TDO

O

JTAG Data Out

On the falling edge of TCK, the TDO is serial data shifted out from either the instruction or data register. When

no data is shifted out, the TDO is tri-stated (high impedance).

TCK

I

JTAG Clock Input

An input test clock used to shift into or out of the boundary-scan register cells. TCK is independent of the sys-

tem and processor clock with nominal 40-60% duty cycle.

TMS

I

JTAG Command Select

The logic signal received at the TMS input is decoded by the TAP controller to control test operation. TMS is

sampled on the rising edge of TCK. An external pull-up resistor is required.

TRST*

I

JTAG Reset

The TRST* pin is an active-low signal used for asynchronous reset of the debug unit, independent of the pro-

cessor logic. During normal CPU operation, the JTAG controller will be held in the reset mode, asserting this

active low pin.

When asserted low, this pin will also tristate the TDO pin. An external pull-down resistor is required.

JTAG32*

I

JTAG 32-bit scan

This pin is used to control length of the scan chain for SysAD (32-bit or 64-bit) for the JTAG mode. When set

to Vss, 32-bit bus mode is selected. In this mode, only SysAD(31:0) are part of the scan chain. When set to

Vcc, 64-bit bus mode is selected. In this mode, SysAD(63:0) are part of the scan chain. This pin has a built-in

pull-down device to guarantee 32-bit scan, if it is left un connected.

JR_V

cc

I

JTAG VCC

This pin has an internal pull-down to continuously reset the JTAG controller (if left unconnected) bypassing

the TRst* pin. When supplied with Vcc, the TRst* pin will be the primary control for the JTAG reset.

Pin Name

Type

Description

Table 5 Pin Descriptions (Page 2 of 2)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A-1001E | SINGLE DIGIT DISPLAY |

| A-811H | SINGLE DIGIT DISPLAY |

| A-811SR | SINGLE DIGIT DISPLAY |

| A-811Y | SINGLE DIGIT DISPLAY |

| A-1001G | SINGLE DIGIT DISPLAY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 79RC64T574-200DZ | 制造商:Integrated Device Technology Inc 功能描述:MPU RC64574 RISC 64-Bit 200MHz 3.3V 128-Pin PQFP |

| 79RC64T574-250DZ | 制造商:Integrated Device Technology Inc 功能描述:MPU RC64574 RISC 64-Bit 250MHz 3.3V 128-Pin PQFP |

| 79RC64T575-200DP | 制造商:Integrated Device Technology Inc 功能描述:MPU RC64575 RISC 64-Bit 200MHz 3.3V 208-Pin PQFP |

| 79RC64T575-250DP | 制造商:Integrated Device Technology Inc 功能描述:MPU RC64575 RISC 64-Bit 250MHz 3.3V 208-Pin PQFP 制造商:IDT from Components Direct 功能描述:64BIT EMBEDDED MICROPROCESSOR RC64575 RISC 250MHZ - Trays 制造商:IDT 功能描述:IDT 79RC64T575-250DP, 64Bit Embedded Microprocessor RC64575 RISC 250MHz 3.3V 208-Pin PQFP |

| 79RC64V474-180DZ | 制造商:Integrated Device Technology Inc 功能描述:MPU RC4000 RISC 64-Bit 180MHz 3.3V 128-Pin PQFP 制造商:IDT from Components Direct 功能描述:79RC64V474-180DZ, 64BIT MICROPROCESSOR RC4000 RISC 180MHZ 3. - Trays 制造商:IDT 功能描述:IDT 79RC64V474-180DZ, 64Bit Microprocessor RC4000 RISC 180MHz 3.3V 128-Pin PQFP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。