- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382826 > 79RC32V364133DAI (INTEGRATED DEVICE TECHNOLOGY INC) RISController Embedded 32-bit Microprocessor, based on RISCore32300 PDF資料下載

參數(shù)資料

| 型號: | 79RC32V364133DAI |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | RISController Embedded 32-bit Microprocessor, based on RISCore32300 |

| 中文描述: | 32-BIT, 133 MHz, RISC PROCESSOR, PQFP144 |

| 封裝: | 20 X 20 MM, 1.40 MM HEIGHT, TQFP-144 |

| 文件頁數(shù): | 7/21頁 |

| 文件大?。?/td> | 370K |

| 代理商: | 79RC32V364133DAI |

7 of 21

June 20, 2000

79RC32364

*Notice: The information in this document is subject to change without notice

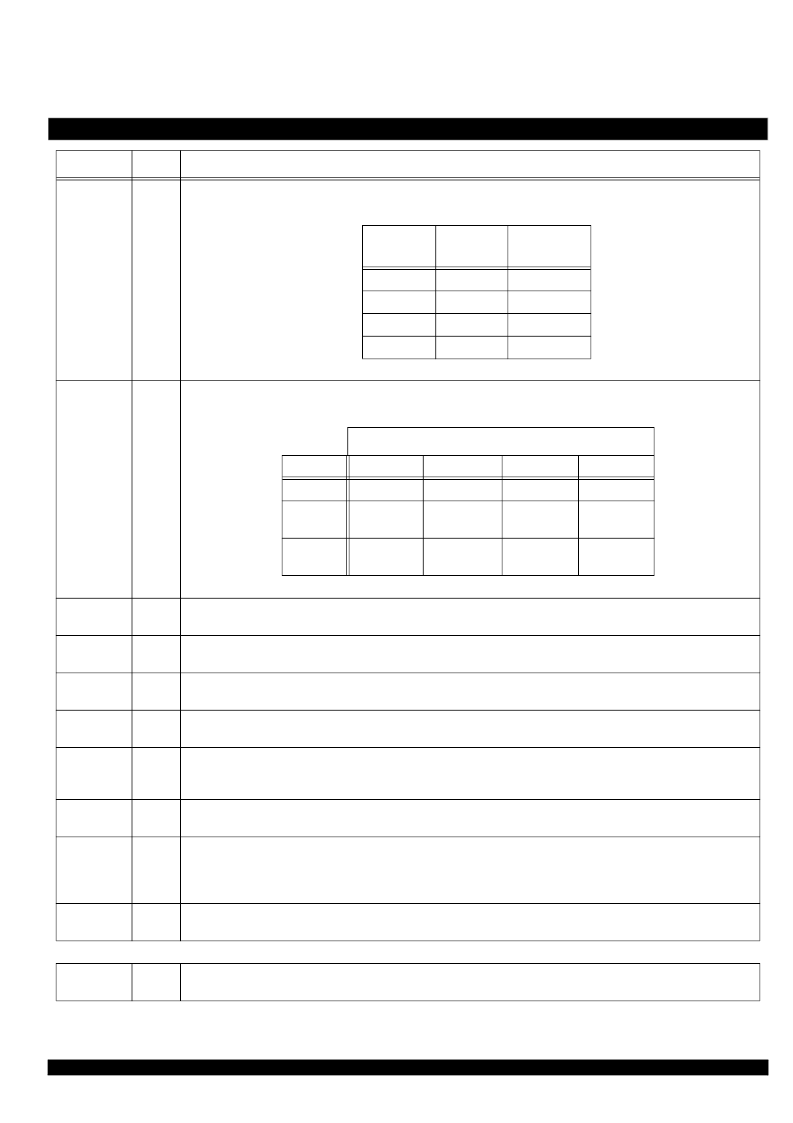

Width(1:0)

O

Bus Width

Indicates the Physical Memory/IO data bus size as follows:

BE*(3:0)

O

ByteEnables(3:0)/Addr(1:0)

Indicates which byte lanes are expected to participate in the transfer.

CIP*

O

Cycle-in-progress

Denotes that a cycle is in progress. Asserted in the address phase and continue asserted until the ACK* for the last data is sampled.

I/D*

O

I/D*

Indicates that the current cycle is for an instruction (active high) or data (active low) transaction.

Rd*

O

Read

This active-low signal indicates that the current transaction is a read.

Wr*

O

Write

This active-low signal indicates that the current cycle transaction is a write.

DataEn*

O

Data Enable

This active-low signal indicates that the AD bus is in data cycle. DEN* is asserted after the address cycle (starting of data cycle), and

deasserted at the end of the last data cycle.

DT/R*

O

Data Transmit/Receive

This active-low signal indicates the current cycle transaction of data direction. “High” is for a write cycle and “Low” is for a read cycle.

Ack*

I

Acknowledge Receiving Data

On read transactions, this signal indicates to the RC32364 that the memory system has placed valid data on the A/D bus, and that

the processor may move the data into the on-chip Read Buffer. On a write transaction, this indicates to the RC32364 that the mem-

ory system has accepted the data on the A/D bus.

Last*

O

Last Data

This active-low output is used to indicate the last data phase of a transfer.

Handshake Interface

BusErr*

I

Bus Error

Indicates that a bus error has occurred.

Pin

Type

Description

Table 3 System Interface Pin Descriptions (Page 2 of 4)

Width(1)

Width(0)

Port

Width

0

0

8 bits

0

1

16 bits

1

0

32 bits

1

1

Reserved

Byte Lanes Enabled In Data Transfer

Port Width

BE(3)

BE(2)

BE(1)

BE(0)

32-bit

Used

Used

Used

Used

16-bit

Byte High

Enable

Not Used

Address Bit 1

(A1)

Byte Low

Enable

8-bit

Not Used

(Driven High)

Not Used

(Driven High)

Address Bit 1

(A1)

Address Bit 0

(A0)

相關PDF資料 |

PDF描述 |

|---|---|

| 79RC32435 | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32H435-266BC | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32H435-266BCI | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32H435-300BC | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32H435-300BCI | IDTTM InterpriseTM Integrated Communications Processor |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 79RC5000 | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:MULTI-ISSUE 64-BIT MICROPROCESSOR |

| 79RC64574 | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:Advanced 64-bit Microprocessors Product Family |

| 79RC64575 | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:Advanced 64-bit Microprocessors Product Family |

| 79RC64T574-200DZ | 制造商:Integrated Device Technology Inc 功能描述:MPU RC64574 RISC 64-Bit 200MHz 3.3V 128-Pin PQFP |

| 79RC64T574-250DZ | 制造商:Integrated Device Technology Inc 功能描述:MPU RC64574 RISC 64-Bit 250MHz 3.3V 128-Pin PQFP |

發(fā)布緊急采購,3分鐘左右您將得到回復。