- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄382826 > 79RC32K438-233BBI (Integrated Device Technology, Inc.) IDTTM InterpriseTM Integrated Communications Processor PDF資料下載

參數(shù)資料

| 型號(hào): | 79RC32K438-233BBI |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | IDTTM InterpriseTM Integrated Communications Processor |

| 中文描述: | IDTTM InterpriseTM集成通信處理器 |

| 文件頁(yè)數(shù): | 5/59頁(yè) |

| 文件大?。?/td> | 644K |

| 代理商: | 79RC32K438-233BBI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)

5 of 59

May 25, 2004

IDT 79RC32438

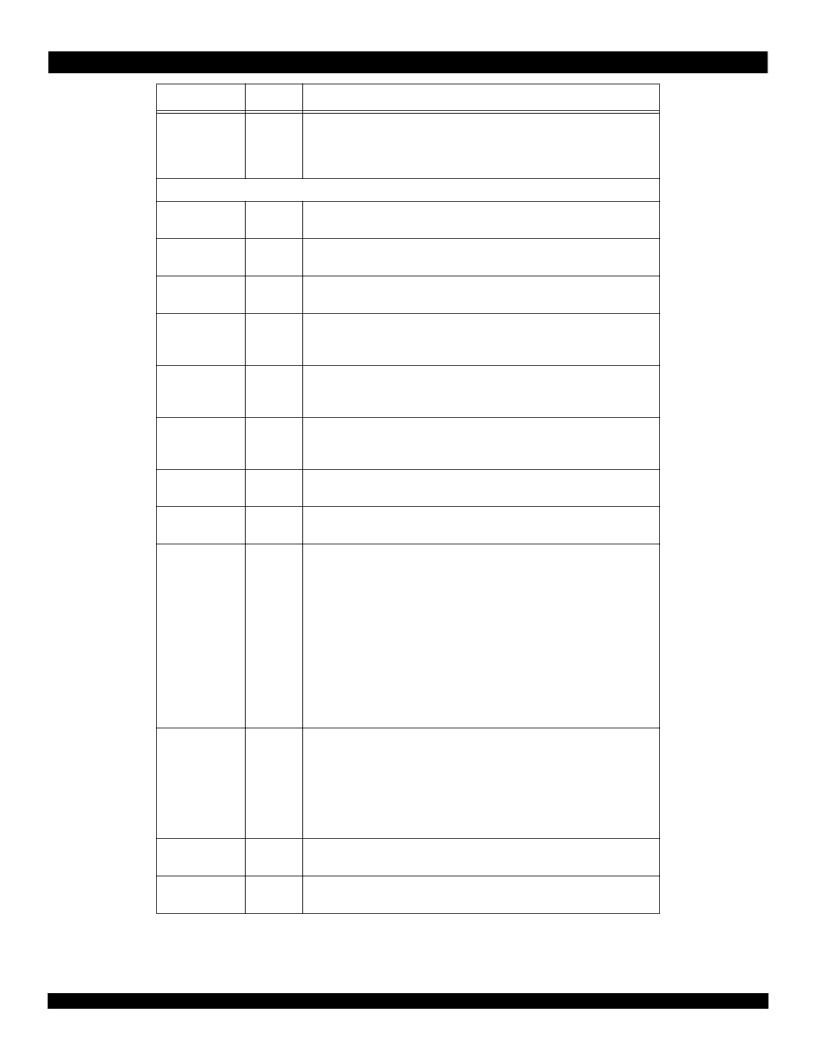

WAITACKN

I

Wait or Transfer Acknowledge.

When configured as wait, this signal is

asserted during a memory and peripheral bus transaction to extend the bus

cycle. When configured as a transfer acknowledge, this signal is asserted during

a transaction to signal the completion of the transaction.

DDR Bus

DDRADDR[13:0]

O

DDR Address Bus.

14-bit multiplexed DDR bus address bus. This bus is used

to transfer the addresses to the DDR devices.

DDRBA[1:0]

O

DDR Bank Address.

These signals are used to transfer the bank address to the

DDRs.

DDRCASN

O

DDR Column Address Strobe.

This signal is asserted during DDR transac-

tions.

DDRCKE

O

DDR Clock Enable.

The DDR clock enable is asserted during normal DDR

operation. This signal is negated during following a cold reset or during a power

down operation.

DDRCKN[1:0]

O

DDR Negative DDR clock.

These signals are the negative clock of the differen-

tial DDR clock pair. Two copies of this output are provided to reduce signal load-

ing.

DDRCKP[1:0]

O

DDR Positive DDR clock.

These signals are the positive clock of the differen-

tial DDR clock pair. Two copies of this output are provided to reduce signal load-

ing.

DDRCSN[1:0]

O

DDR Chip Selects.

These active low signals are used to select DDR device(s)

on the DDR bus.

DDRDATA[31:0]

I/O

DDR Data Bus.

32-bit DDR data bus used to transfer data between the

RC32438 and the DDR devices. Data is transferred on both edges of the clock.

DDRDM[7:0]

O

DDR Data Write Enables.

Byte data write enables used to enable specific byte

lanes during DDR writes.

DDRDM[0] corresponds to DDRDATA[7:0]

DDRDM[1] corresponds to DDRDATA[15:8]

DDRDM[2] corresponds to DDRDATA[23:16]

DDRDM[3] corresponds to DDRDATA[31:24]

DDRDM[4] corresponds to DDRDATA[39:32]

DDRDM[5] corresponds to DDRDATA[47:40]

DDRDM[6] corresponds to DDRDATA[55:48]

DDRDM[7] corresponds to DDRDATA[54:56]

(Refer to the DDR Data Bus Multiplexing section in Chapter 7 of the RC32438

User Reference Manual.)

DDRDQS[3:0]

I/O

DDR Data Strobes.

DDR byte data strobes used to clock data between DDR

devices and the RC32438. These strobes are inputs during DDR reads and out-

puts during DDR writes.

DDRDQS[0] corresponds to DDRDATA[7:0].

DDRDQS[1] corresponds to DDRDATA[15:8].

DDRDQS[2] corresponds to DDRDATA[23:16].

DDRDQS[3] corresponds to DDRDATA[31:24].

DDROEN[3:0]

O

DDR Bus Switch Output Enables.

These pins are used to enable external

data bus switches in systems that support data bus multiplexing.

DDRRASN

O

DDR Row Address Strobe.

The DDR row address strobe is asserted during

DDR transactions.

Signal

Type

Name/Description

Table 1 Pin Description (Part 2 of 9)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 79RC32K438-266BB | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32K438-300BB | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32K438200BB | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32K438200BBI | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32K438233BB | IDTTM InterpriseTM Integrated Communications Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 79RC32K438266BB | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32K438-266BB | 功能描述:處理器 - 專門(mén)應(yīng)用 RoHS:否 制造商:Freescale Semiconductor 類(lèi)型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| 79RC32K438-266BBG | 功能描述:處理器 - 專門(mén)應(yīng)用 RoHS:否 制造商:Freescale Semiconductor 類(lèi)型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| 79RC32K438-266BBGI | 功能描述:處理器 - 專門(mén)應(yīng)用 RoHS:否 制造商:Freescale Semiconductor 類(lèi)型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| 79RC32K438266BBI | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:IDTTM InterpriseTM Integrated Communications Processor |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。