- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382826 > 79RC32H435-350BC (Integrated Device Technology, Inc.) IDTTM InterpriseTM Integrated Communications Processor PDF資料下載

參數(shù)資料

| 型號(hào): | 79RC32H435-350BC |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | IDTTM InterpriseTM Integrated Communications Processor |

| 中文描述: | IDTTM InterpriseTM集成通信處理器 |

| 文件頁(yè)數(shù): | 4/53頁(yè) |

| 文件大?。?/td> | 444K |

| 代理商: | 79RC32H435-350BC |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)

4 of 53

January 19, 2006

IDT 79RC32435

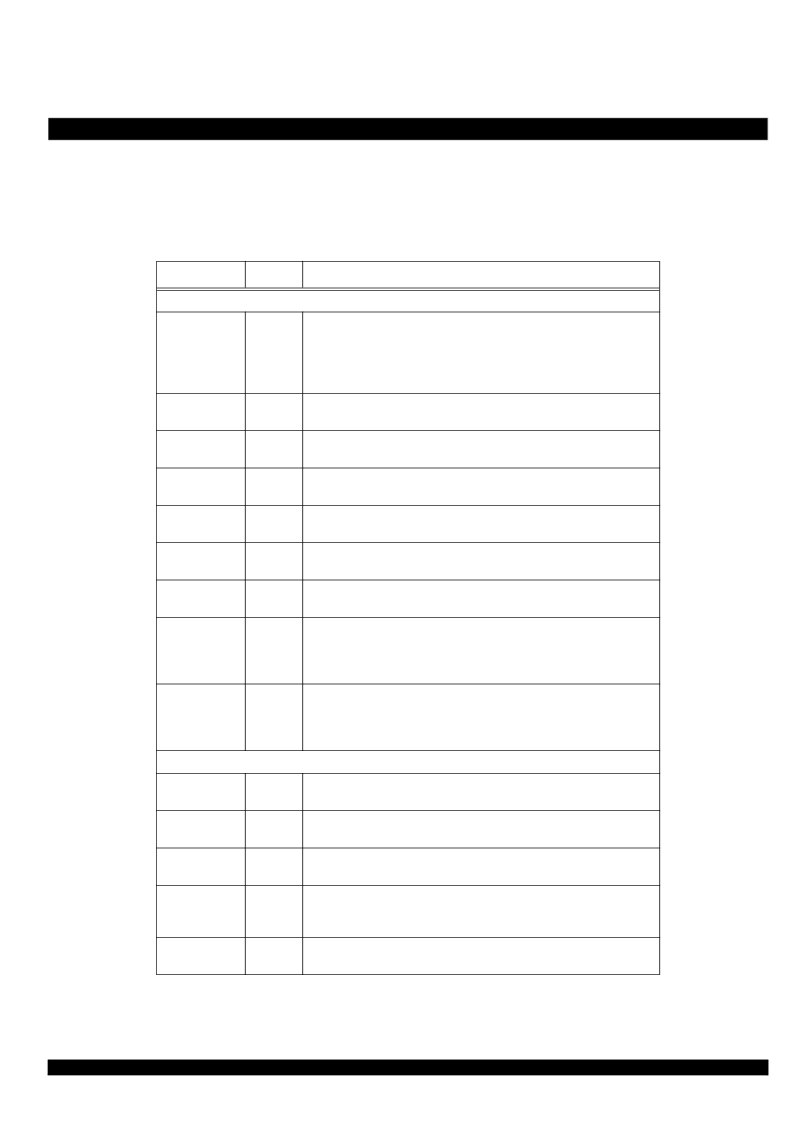

Pin Desc ription Table

The following table lists the functions of the pins provided on the RC32435. Some of the functions listed may be multiplexed onto the same pin.

The active polarity of a signal is defined using a suffix. Signals ending with an “N” are defined as being active, or asserted, when at a logic zero

(low) level. All other signals (including clocks, buses, and select lines) will be interpreted as being active, or asserted, when at a logic one (high) level.

S ignal

Type

Name/Desc ription

Memory and Peripheral Bus

BDIRN

O

External Buffer Direction.

Controls the direction of the external data bus buffer

for the memory and peripheral bus. If the RC32435 memory and peripheral bus

is connected to the A side of a transceiver, such as an IDT74FCT245, then this

pin may be directly connected to the direction control (e.g., BDIR) pin of the

transceiver.

BOEN

O

External Buffer Enable.

This signal provides an output enable control for an

external buffer on the memory and peripheral data bus.

WEN

O

Write Enables.

This signal is the memory and peripheral bus write enable sig-

nal.

CSN[3:0]

O

Chip Selects.

These signals are used to select an external device on the mem-

ory and peripheral bus.

MADDR[21:0]

O

Address Bus.

22-bit memory and peripheral bus address bus.

MADDR[25:22] are available as GPIO alternate functions.

MDATA[7:0]

I/O

Data Bus.

8-bit memory and peripheral data bus. During a cold reset, these pins

function as inputs that are used to load the boot configuration vector.

OEN

O

Output Enable.

This signal is asserted when data should be driven by an exter-

nal device on the memory and peripheral bus.

RWN

O

Read Write.

This signal indicates whether the transaction on the memory and

peripheral bus is a read transaction or a write transaction. A high level indicates

a read froman external device. A low level indicates a write to an external

device.

WAITACKN

I

Wait or Transfer Acknowledge.

When configured as wait, this signal is

asserted during a memory and peripheral bus transaction to extend the bus

cycle. When configured as a transfer acknowledge, this signal is asserted during

a transaction to signal the completion of the transaction.

DDR Bus

DDRADDR[13:0]

O

DDR Address Bus.

14-bit multiplexed DDR address bus. This bus is used to

transfer the addresses to the DDR devices.

DDRBA[1:0]

O

DDR Bank Address.

These signals are used to transfer the bank address to the

DDRs.

DDRCASN

O

DDR Column Address Strobe.

This signal is asserted during DDR transac-

tions.

DDRCKE

O

DDR Clock Enable.

The DDR clock enable signal is asserted during normal

DDR operation. This signal is negated following a cold reset or during a power

down operation.

DDRCKN

O

DDR Negative DDR clock.

This signal is the negative clock of the differential

DDR clock pair.

Table 1 Pin Description (Part 1 of 6)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 79RC32H435-350BCI | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32H435-400BC | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32H435-400BCI | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32438 | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32K438-200BB | IDTTM InterpriseTM Integrated Communications Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 79RC32H435-350BCG | 功能描述:處理器 - 專門應(yīng)用 RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| 79RC32H435-350BCGI | 功能描述:處理器 - 專門應(yīng)用 RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| 79RC32H435-350BCI | 制造商:Integrated Device Technology Inc 功能描述:MPU RC32435 RISC 32-Bit 350MHz 2.5V/3.3V 256-Pin CABGA 制造商:Integrated Device Technology Inc 功能描述:COMMUNICATIONS PROCESSOR 256CABGA - Bulk |

| 79RC32H435-400BC | 功能描述:處理器 - 專門應(yīng)用 RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| 79RC32H435-400BCG | 功能描述:處理器 - 專門應(yīng)用 RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。