- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382826 > 79RC32H435-300BCI (Integrated Device Technology, Inc.) IDTTM InterpriseTM Integrated Communications Processor PDF資料下載

參數(shù)資料

| 型號: | 79RC32H435-300BCI |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | IDTTM InterpriseTM Integrated Communications Processor |

| 中文描述: | IDTTM InterpriseTM集成通信處理器 |

| 文件頁數(shù): | 16/53頁 |

| 文件大?。?/td> | 444K |

| 代理商: | 79RC32H435-300BCI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁

16 of 53

January 19, 2006

IDT 79RC32435

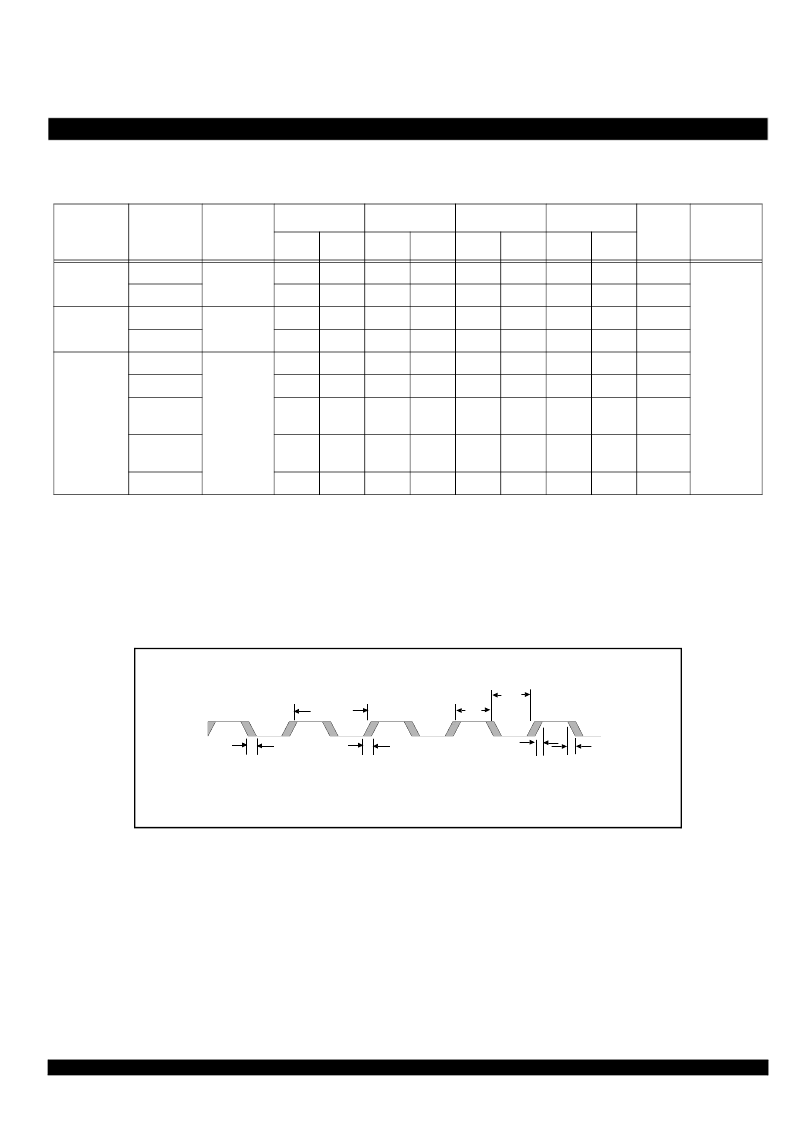

S ystem Clock Parameters

(Values based on systems running at recommended supply voltages and operating temperatures, as shown in Tables 15 and 16.)

Figure 3 Clock Parameters Waveform

Parameter

S ymbol

Referenc e

Edge

266MHz

300MHz

350MHz

400MHz

Units

T iming

Diagram

Referenc e

Mn

Max

Mn

Max

Min

Max

Mn

Max

PCLK

1

1.

The CPU pipeline clock (PCLK) speed is selected during cold reset by the boot configuration vector (see Table 3). Refer to Chapter 3, Clocking and Initialization, in the RC32435

User Reference Manual for the allowable frequency ranges of CLK and PCLK.

2.

ICLK is the internal IPBus clock. It is always equal to PCLK divided by 2. This clock cannot be sampled externally.

3.

The ethernet clock (MIIxRXCLK and MIIxTXCLK) frequency must be equal to or less than 1/2 ICLK (MIIxRXCLK and MIIxTXCLK <= 1/2(ICLK)).

4.

PCICLK must be equal to or less than two times ICLK (PCICLK <= 2(ICLK)) with a maximumPCICLK of 66 MHz.

5.

The input clock (CLK) is input fromthe external oscillator to the internal PLL.

Frequency

none

200

266

200

300

200

350

200

400

MHz

See Figure 3.

Tper

3.8

5.0

3.3

5.0

2.85

5.0

2.5

5.0

ns

ICLK

2,3,4

Frequency

none

100

133

100

150

100

175

100

200

MHz

Tper

7.5

10.0

6.7

10.0

5.7

10.0

5.0

10.0

ns

CLK

5

Frequency

none

25

125

25

125

25

125

25

125

MHz

Tper_5a

8.0

40.0

8.0

40.0

8.0

40.0

8.0

40.0

ns

Thigh_5a,

Tlow_5a

40

60

40

60

40

60

40

60

% of

Tper_5a

Trise_5a,

Tfall_5a

—

3.0

—

3.0

—

3.0

—

3.0

ns

Tjitter_5a

—

0.1

—

0.1

—

0.1

—

0.1

ns

Table 5 Clock Parameters

Tlow_5a

Thigh_5a

Tper_5a

CLK

Trise_5a

Tfall_5a

Tjitter_5a

Tjitter_5a

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 79RC32H435-350BC | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32H435-350BCI | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32H435-400BC | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32H435-400BCI | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32438 | IDTTM InterpriseTM Integrated Communications Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 79RC32H435-350BC | 功能描述:處理器 - 專門應(yīng)用 RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| 79RC32H435-350BCG | 功能描述:處理器 - 專門應(yīng)用 RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| 79RC32H435-350BCGI | 功能描述:處理器 - 專門應(yīng)用 RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| 79RC32H435-350BCI | 制造商:Integrated Device Technology Inc 功能描述:MPU RC32435 RISC 32-Bit 350MHz 2.5V/3.3V 256-Pin CABGA 制造商:Integrated Device Technology Inc 功能描述:COMMUNICATIONS PROCESSOR 256CABGA - Bulk |

| 79RC32H435-400BC | 功能描述:處理器 - 專門應(yīng)用 RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。