- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360503 > 74LVT16652A (NXP Semiconductors N.V.) 4-Line To 10-Line Decoders (1 of 10) 16-PDIP -40 to 85 PDF資料下載

參數(shù)資料

| 型號: | 74LVT16652A |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | 4-Line To 10-Line Decoders (1 of 10) 16-PDIP -40 to 85 |

| 中文描述: | 3.3V的小型終端16位總線收發(fā)器/寄存器三態(tài) |

| 文件頁數(shù): | 4/12頁 |

| 文件大小: | 101K |

| 代理商: | 74LVT16652A |

Philips Semiconductors

Product specification

74LVT16652A

3.3V 16-bit bus transceiver/register (3-State)

1998 Feb 19

4

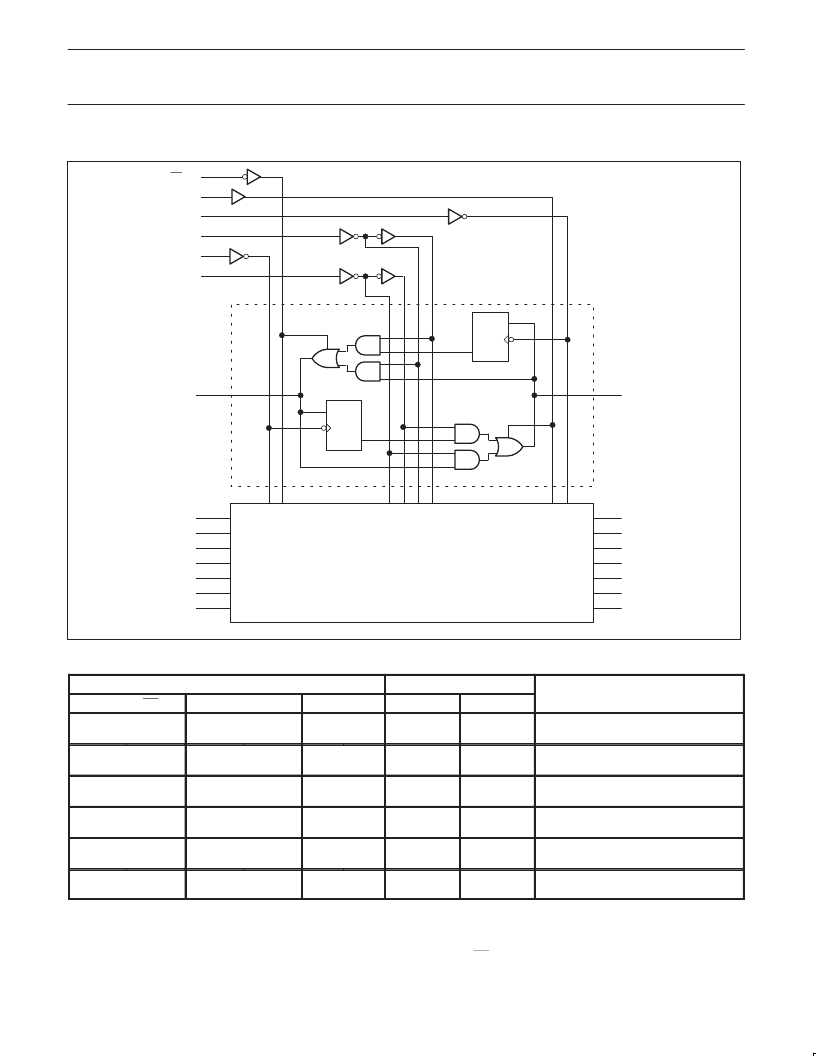

LOGIC DIAGRAM

1D

C1

Q

DETAIL A X 7

nB0

1D

C1

Q

nA0

1of 8 Channels

nA7

nA6

nA5

nA4

nA3

nA2

nA1

nB1

nB2

nB3

nB4

nB5

nB6

nB7

nOEBA

nOEAB

nCPBA

nSBA

nCPAB

nSAB

SH00065

FUNCTION TABLE

INPUTS

DATA I/O

OPERATING MODE

nOEAB

nOEBA

nCPAB

nCPBA

nSAB

nSBA

nAx

nBx

L

L

H

H

H or L

↑

H or L

↑

X

X

X

X

Input

Input

Isolation

Store A and B data

X

H

H

H

↑

↑

H or L

↑

X

**

X

X

Input

Unspecified

output*

Store A, Hold B

Store A in both registers

L

L

X

L

H or L

↑

↑

↑

X

X

X

**

Unspecified

output*

Input

Hold A, Store B

Store B in both registers

L

L

L

L

X

X

X

H or L

X

X

L

H

Output

Input

Real time B data to A bus

Stored B data to A bus

H

H

H

H

X

H or L

X

X

L

H

X

X

Input

Output

Real time A data to B bus

Store A data to B bus

H

L

H or L

H or L

H

H

Output

Output

Stored A data to B bus

Stored B data to A bus

H =

L

X =

↑

=

*

High voltage level

Low voltage level

Don’t care

Low-to-High clock transition

The data output function may be enabled or disabled by various signals at the nOEBA and nOEAB inputs. Data input functions are

always enabled, i.e., data at the bus pins will be stored on every Low-to-High transition of the clock.

If both Select controls (nSAB and nSBA) are Low, then clocks can occur simultaneously. If either Select control is High, the clocks must

be staggered in order to load both registers.

=

**

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74LVT20 | 4-Line To 10-Line Decoders (1 of 10) 16-SO -40 to 85 |

| 74LVT20D | 3.3V Dual 4-input NAND gate |

| 74LVT20DB | 3.3V Dual 4-input NAND gate |

| 74LVT20PW | 8-Channel Analog Multiplexer/Demultiplexer with Injection-Current Effect Control 16-SOIC -40 to 125 |

| 74LVT20PWDH | 8-Channel Analog Multiplexer/Demultiplexer with Injection-Current Effect Control 16-SOIC -40 to 125 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74LVT16652ADG | 功能描述:總線收發(fā)器 3.3V 16-BIT REG XCVR 3S RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| 74LVT16652ADGG,112 | 功能描述:總線收發(fā)器 3.3V 16-BIT REG RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| 74LVT16652ADGG,118 | 功能描述:總線收發(fā)器 3.3V 16-BIT REG RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| 74LVT16652ADG-T | 功能描述:總線收發(fā)器 3.3V 16-BIT REG XCVR 3S RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| 74LVT16652ADL | 功能描述:總線收發(fā)器 3.3V 16-BIT BUS XCVR 3-S RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。