- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360483 > 74LV08PWDH (NXP SEMICONDUCTORS) Quad 2-input AND gate PDF資料下載

參數(shù)資料

| 型號: | 74LV08PWDH |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 通用總線功能 |

| 英文描述: | Quad 2-input AND gate |

| 中文描述: | LV/LV-A/LVX/H SERIES, QUAD 2-INPUT AND GATE, PDSO14 |

| 封裝: | 4.40 MM, PLASTIC, TSSOP-14 |

| 文件頁數(shù): | 2/10頁 |

| 文件大小: | 104K |

| 代理商: | 74LV08PWDH |

Philips Semiconductors

Product specification

74LV08

Quad 2-input AND gate

2

1998 Apr 20

853–1893 19256

FEATURES

Wide operating voltage: 1.0 to 5.5 V

Optimized for Low Voltage applications: 1.0 to 3.6 V

Accepts TTL input levels between V

CC

= 2.7 V and V

CC

= 3.6 V

Typical V

OLP

(output ground bounce) < 0.8 V at V

CC

= 3.3 V,

T

amb

= 25

°

C.

Typical V

OHV

(output V

OH

undershoot) > 2 V at V

CC

= 3.3 V,

T

amb

= 25

°

C.

Output capability: standard

I

CC

category: SSI

DESCRIPTION

The 74LV08 is a low-voltage Si-gate CMOS device and is pin and

function compatible with 74HC/HCT08.

The 74LV08 provides the 2-input AND function.

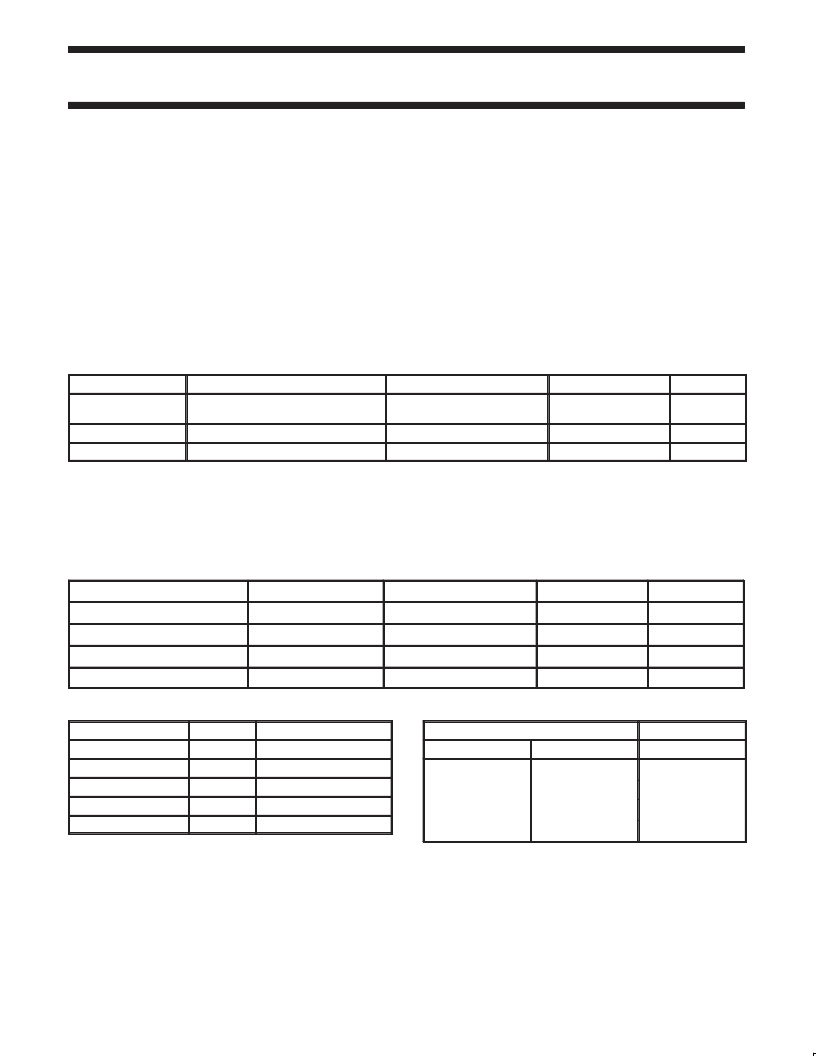

QUICK REFERENCE DATA

GND = 0 V; T

amb

= 25

°

C; t

r

= t

f

SYMBOL

2.5 ns

PARAMETER

CONDITIONS

TYPICAL

UNIT

t

PHL

/t

PLH

Propagation delay

nA, nB to nY

C

L

= 15 pF;

V

CC

= 3.3 V

7

ns

C

I

C

PD

Input capacitance

3.5

pF

Power dissipation capacitance per gate

See Notes 1 and 2

10

pF

NOTES:

1. C

PD

is used to determine the dynamic power dissipation (P

D

in

μ

W)

P

D

= C

PD

V

CC2

f

i

(C

L

f

i

= input frequency in MHz; C

L

= output load capacitance in pF;

f

o

= output frequency in MHz; V

CC

= supply voltage in V;

(C

L

V

CC2

f

o

) = sum of the outputs.

2. The condition is V

I

= GND to V

CC.

V

CC2

f

o

) where:

ORDERING INFORMATION

PACKAGES

TEMPERATURE RANGE

OUTSIDE NORTH AMERICA

NORTH AMERICA

PKG. DWG. #

14-Pin Plastic DIL

–40

°

C to +125

°

C

74LV08 N

74LV08 N

SOT27-1

14-Pin Plastic SO

–40

°

C to +125

°

C

74LV08 D

74LV08 D

SOT108-1

14-Pin Plastic SSOP Type II

–40

°

C to +125

°

C

74LV08 DB

74LV08 DB

SOT337-1

14-Pin Plastic TSSOP Type I

–40

°

C to +125

°

C

74LV08 PW

74LV08PW DH

SOT402-1

PIN DESCRIPTION

PIN NUMBER

SYMBOL

FUNCTION

1, 4, 9, 12

1A – 4A

Data inputs

2, 5, 10, 13

1Y – 4B

Data inputs

3, 6, 8, 11

1Y – 4Y

Data outputs

7

GND

Ground (0 V)

14

V

CC

Positive supply voltage

FUNCTION TABLE

INPUTS

OUTPUTS

nA

nB

nY

L

L

L

L

H

L

H

L

L

H

H

H

NOTES:

H = HIGH voltage level

L = LOW voltage level

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74LV08 | Quad 2-input AND gate |

| 74LV107DB-T | J-K-Type Flip-Flop |

| 74LV107D-T | J-K-Type Flip-Flop |

| 74LV107PW-T | J-K-Type Flip-Flop |

| 74LV109DB-T | J-K-Type Flip-Flop |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74LV08PW-Q100,118 | 制造商:NXP Semiconductors 功能描述:AND Gate 4-Element 2-IN CMOS 14-Pin TSSOP T/R 制造商:NXP Semiconductors 功能描述:74LV08PW-Q100/TSSOP14/REEL13// - Tape and Reel 制造商:NXP Semiconductors 功能描述:IC GATE AND QUAD 2INPUT 14TSSOP |

| 74LV08PW-T | 功能描述:邏輯門 QUAD 2-INPUT AND GATE 3-VOLT RoHS:否 制造商:Texas Instruments 產(chǎn)品:OR 邏輯系列:LVC 柵極數(shù)量:2 線路數(shù)量(輸入/輸出):2 / 1 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 傳播延遲時間:3.8 ns 電源電壓-最大:5.5 V 電源電壓-最小:1.65 V 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DCU-8 封裝:Reel |

| 74LV10 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Triple 3-input NAND gate |

| 74LV107 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Dual JK flip-flop with reset; negative-edge trigger |

| 74LV107D | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Dual JK flip-flop with reset; negative-edge trigger |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。