- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360460 > 74HCT280 (NXP Semiconductors N.V.) 9-bit odd/even parity generator/checker(9位奇/偶發(fā)生器/檢測器) PDF資料下載

參數(shù)資料

| 型號: | 74HCT280 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | 9-bit odd/even parity generator/checker(9位奇/偶發(fā)生器/檢測器) |

| 中文描述: | 9位奇/偶校驗發(fā)生器/檢查(9位奇/偶發(fā)生器/檢測器) |

| 文件頁數(shù): | 2/7頁 |

| 文件大小: | 49K |

| 代理商: | 74HCT280 |

December 1990

2

Philips Semiconductors

Product specification

9-bit odd/even parity generator/checker

74HC/HCT280

FEATURES

Word-length easily expanded by cascading

Similar pin configuration to the “180” for easy system

up-grading

Generates either odd or even parity for nine data bits

Output capability: standard

I

CC

category: MSI

GENERAL DESCRIPTION

The 74HC/HCT280 are high-speed Si-gate CMOS devices

and are pin compatible with low power Schottky TTL

(LSTTL). They are specified in compliance with JEDEC

standard no. 7A.

The 74HC/HCT280 are 9-bit parity generators or checkers

commonly used to detect errors in high-speed data

transmission or data retrieval systems. Both even and odd

parity outputs are available for generating or checking

even or odd parity up to 9 bits.

The even parity output (

∑

E

) is HIGH when an even number

of data inputs (I

0

to I

8

) are HIGH. The odd parity output (

∑

0

)

is HIGH when an odd number of data inputs are HIGH.

Expansion to larger word sizes is accomplished by tying

the even outputs (

∑

E

) of up to nine parallel devices to the

data inputs of the final stage. For a single-chip 16-bit

even/odd parity generator/checker, see

PC74HC/HCT7080.

APPLICATIONS

25-line parity generator/checker

81-line parity generator/checker

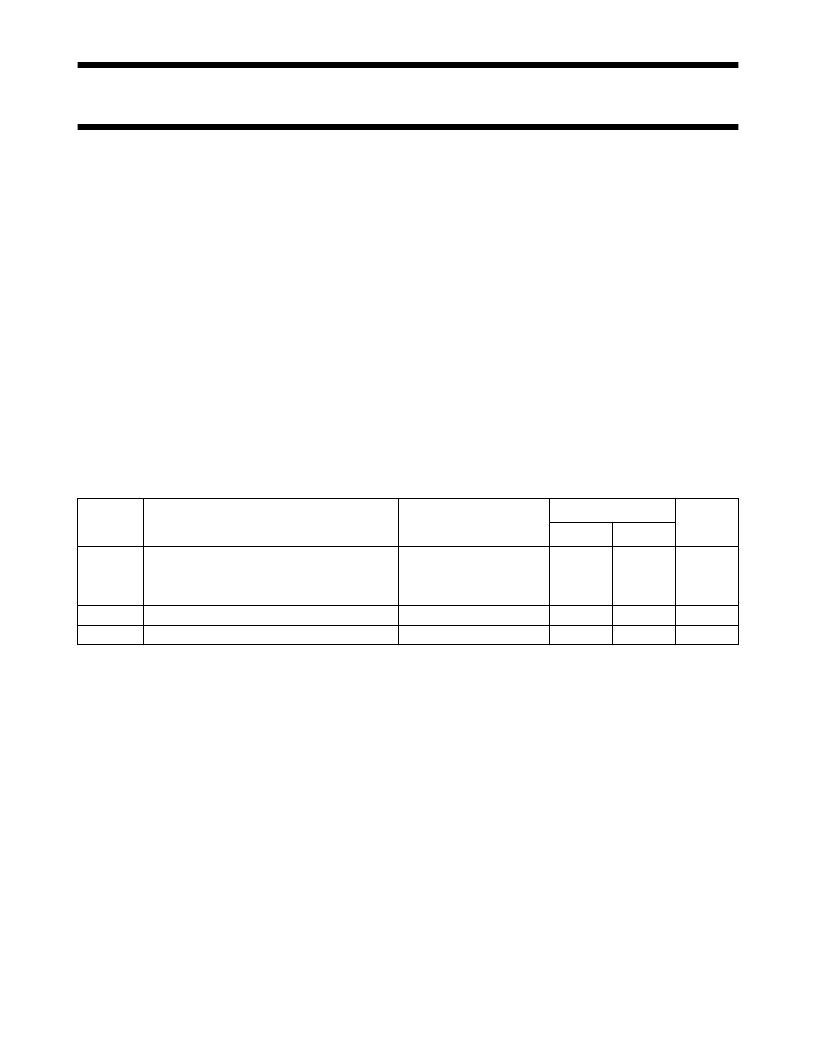

QUICK REFERENCE DATA

GND = 0 V; T

amb

= 25

°

C; t

r

= t

f

= 6 ns

Notes

1.

C

PD

is used to determine the dynamic power dissipation (P

D

in

μ

W):

P

D

= C

PD

×

V

CC2

×

f

i

+ ∑

(C

L

×

V

CC2

×

f

o

) where:

f

i

= input frequency in MHz

f

o

= output frequency in MHz

∑

(C

L

×

V

CC2

×

f

o

) = sum of outputs

C

L

= output load capacitance in pF

V

CC

= supply voltage in V

For HC the condition is V

I

= GND to V

CC

For HCT the condition is V

I

= GND to V

CC

1.5 V

2.

ORDERING INFORMATION

See

“74HC/HCT/HCU/HCMOS Logic Package Information”

.

SYMBOL

PARAMETER

CONDITIONS

TYPICAL

UNIT

HC

HCT

t

PHL

/ t

PLH

propagation delay

I

n

to

∑

E

I

n

to

∑

O

input capacitance

power dissipationcapacitance per package

C

L

= 15 pF; V

CC

= 5 V

17

20

3.5

65

18

22

3.5

65

ns

ns

pF

pF

C

I

C

PD

notes 1 and 2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74HC297 | Digital phase-locked-loop filter |

| 74HCT297 | Digital phase-locked-loop filter |

| 74HC32 | PROTECT HEADER RT ANG 20 CONTACT |

| 74HCT32 | HEADER, 10 POS,0.100 C, DUAL, RT ANG |

| 74HCT32 | 8-Bit Parallel-Out Serial Shift Registers 14-TSSOP -40 to 85 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74HCT280D | 功能描述:奇偶功能 9-BIT PARITY GEN/CHK RoHS:否 制造商:Texas Instruments 電路數(shù)量:1 位數(shù):9 邏輯系列:74AC 封裝 / 箱體:SOIC-14 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:263 ns 工作電源電壓:1.8 V, 2.5 V, 3.3 V, 5 V 最大工作溫度:+ 70 C 最小工作溫度:- 55 C 封裝:Reel |

| 74HCT280D,652 | 功能描述:奇偶功能 9-BIT PARITY GEN/CHK RoHS:否 制造商:Texas Instruments 電路數(shù)量:1 位數(shù):9 邏輯系列:74AC 封裝 / 箱體:SOIC-14 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:263 ns 工作電源電壓:1.8 V, 2.5 V, 3.3 V, 5 V 最大工作溫度:+ 70 C 最小工作溫度:- 55 C 封裝:Reel |

| 74HCT280D,653 | 功能描述:奇偶功能 9-BIT ODD/EVEN PAR GEN/CHECKER RoHS:否 制造商:Texas Instruments 電路數(shù)量:1 位數(shù):9 邏輯系列:74AC 封裝 / 箱體:SOIC-14 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:263 ns 工作電源電壓:1.8 V, 2.5 V, 3.3 V, 5 V 最大工作溫度:+ 70 C 最小工作溫度:- 55 C 封裝:Reel |

| 74HCT280DB | 功能描述:奇偶功能 9-BIT ODD/EVEN PAR GEN/CHECKER RoHS:否 制造商:Texas Instruments 電路數(shù)量:1 位數(shù):9 邏輯系列:74AC 封裝 / 箱體:SOIC-14 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:263 ns 工作電源電壓:1.8 V, 2.5 V, 3.3 V, 5 V 最大工作溫度:+ 70 C 最小工作溫度:- 55 C 封裝:Reel |

| 74HCT280DB,112 | 功能描述:奇偶功能 9-BIT ODD/EVEN PAR RoHS:否 制造商:Texas Instruments 電路數(shù)量:1 位數(shù):9 邏輯系列:74AC 封裝 / 箱體:SOIC-14 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:263 ns 工作電源電壓:1.8 V, 2.5 V, 3.3 V, 5 V 最大工作溫度:+ 70 C 最小工作溫度:- 55 C 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。