- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370125 > 74F373SC (NATIONAL SEMICONDUCTOR CORP) Octal Transparent Latch with TRI-STATE Outputs PDF資料下載

參數(shù)資料

| 型號(hào): | 74F373SC |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | 通用總線功能 |

| 英文描述: | Octal Transparent Latch with TRI-STATE Outputs |

| 中文描述: | F/FAST SERIES, 8-BIT DRIVER, TRUE OUTPUT, PDSO20 |

| 封裝: | 0.300 INCH, PLASTIC, SOIC-20 |

| 文件頁數(shù): | 2/8頁 |

| 文件大小: | 174K |

| 代理商: | 74F373SC |

Unit Loading/Fan Out

54F/74F

Pin Names

Description

U.L.

Input I

IH

/I

IL

Output I

OH

/I

OL

HIGH/LOW

D

0

–D

7

LE

OE

O

0

–O

7

Data Inputs

Latch Enable Input (Active HIGH)

Output Enable Input (Active LOW)

TRI-STATE Latch Outputs

1.0/1.0

1.0/1.0

1.0/1.0

150/40 (33.3)

20

m

A/

b

0.6 mA

20

m

A/

b

0.6 mA

20

m

A/

b

0.6 mA

b

3 mA/24 mA (20 mA)

Functional Description

The ’F373 contains eight D-type latches with TRI-STATE

output buffers. When the Latch Enable (LE) input is HIGH,

data on the D

n

inputs enters the latches. In this condition

the latches are transparent, i.e., a latch output will change

state each time its D input changes. When LE is LOW, the

latches store the information that was present on the D in-

puts a setup time preceding the HIGH-to-LOW transition of

LE. The TRI-STATE buffers are controlled by the Output

Enable (OE) input. When OE is LOW, the buffers are in the

bi-state mode. When OE is HIGH the buffers are in the high

impedance mode but this does not interfere with entering

new data into the latches.

Truth Table

Inputs

Output

LE

OE

D

n

O

n

H

H

L

X

L

L

L

H

H

L

X

X

H

L

O

n

(no change)

Z

H

e

HIGH Voltage Level

L

e

LOW Voltage Level

X

e

Immaterial

Z

e

High Impedance State

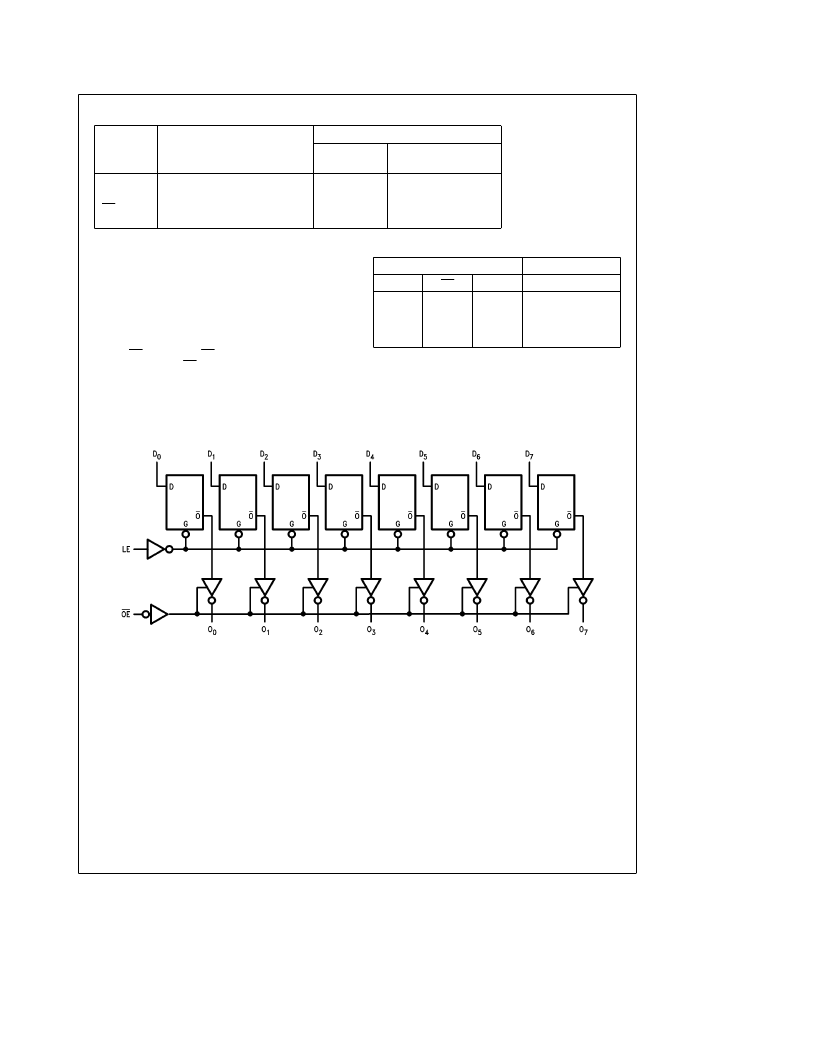

Logic Diagram

TL/F/9523–5

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74F373MSA | Octal Transparent Latch with 3-STATE Outputs |

| 74F373 | Octal Transparent Latch with 3-STATE Outputs |

| 74F373PC | Octal Transparent Latch with 3-STATE Outputs |

| 74F373SJ | Octal Transparent Latch with 3-STATE Outputs |

| 74F373SC | Octal Transparent Latch with 3-STATE Outputs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74F373SC_Q | 功能描述:閉鎖 Octal Trans Latch RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時(shí)間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| 74F373SCX | 功能描述:閉鎖 Octal Trans Latch RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時(shí)間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| 74F373SJ | 功能描述:閉鎖 Octal Trans Latch RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時(shí)間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| 74F373SJ_Q | 功能描述:閉鎖 Octal Trans Latch RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時(shí)間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| 74F373SJX | 功能描述:閉鎖 Octal Trans Latch RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時(shí)間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。