- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370125 > 74F299SC (NATIONAL SEMICONDUCTOR CORP) Octal Universal Shift/Storage Register with Common Parallel I/O Pins PDF資料下載

參數(shù)資料

| 型號(hào): | 74F299SC |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | 通用總線功能 |

| 英文描述: | Octal Universal Shift/Storage Register with Common Parallel I/O Pins |

| 中文描述: | F/FAST SERIES, 8-BIT BIDIRECTIONAL PARALLEL IN PARALLEL OUT SHIFT REGISTER, TRUE OUTPUT, PDSO20 |

| 封裝: | 0.300 INCH, PLASTIC, SOIC-20 |

| 文件頁(yè)數(shù): | 2/10頁(yè) |

| 文件大小: | 194K |

| 代理商: | 74F299SC |

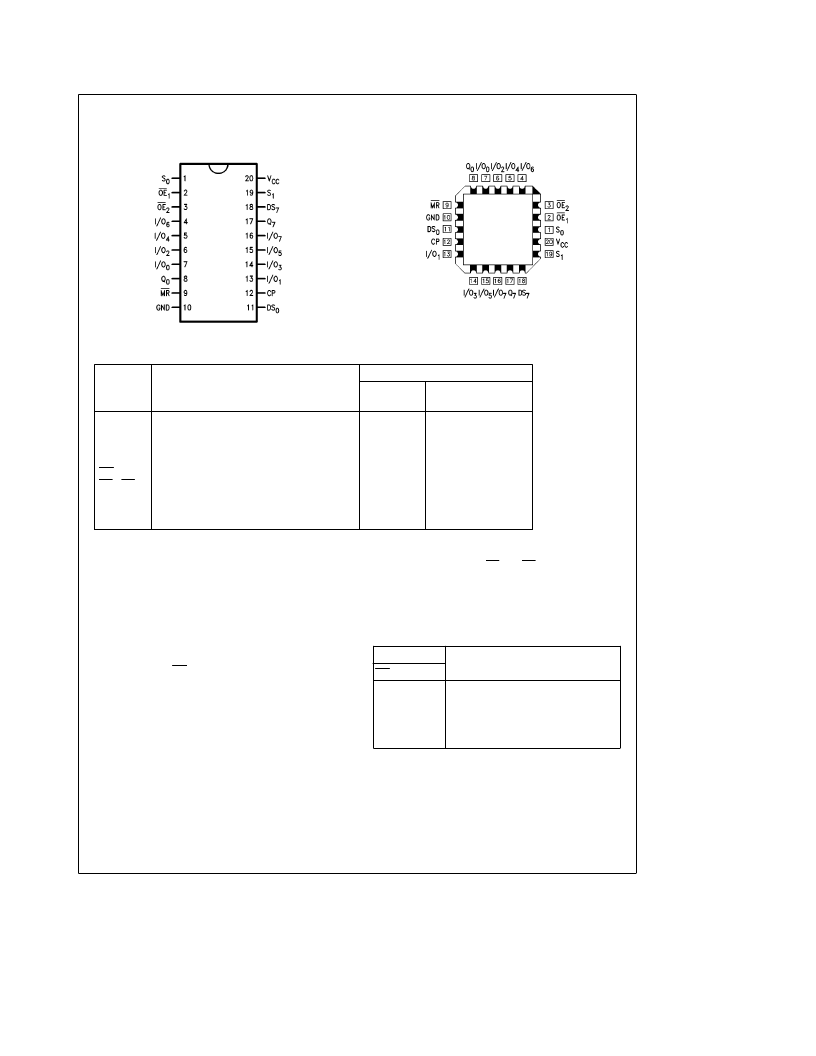

Connection Diagrams

Pin Assignment

for DIP, SOIC and Flatpak

TL/F/9515–2

Pin Assignment

for LCC

TL/F/9515–3

Unit Loading/Fan Out

54F/74F

Pin Names

Description

U.L.

Input I

IH

/I

IL

Output I

OH

/I

OL

HIGH/LOW

CP

DS

0

DS

7

S

0

, S

1

MR

OE

1

, OE

2

I/O

0

–I/O

7

Clock Pulse Input (Active Rising Edge)

Serial Data Input for Right Shift

Serial Data Input for Left Shift

Mode Select Inputs

Asynchronous Master Reset Input (Active LOW)

TRI-STATE Output Enable Inputs (Active LOW)

Parallel Data Inputs or

TRI-STATE Parallel Outputs

Serial Outputs

1.0/1.0

1.0/1.0

1.0/1.0

1.0/2.0

1.0/1.0

1.0/1.0

3.5/1.083

150/40(33.3)

50/33.3

20

m

A/

b

0.6 mA

20

m

A/

b

0.6 mA

20

m

A/

b

0.6 mA

20

m

A/

b

1.2 mA

20

m

A/

b

0.6 mA

20

m

A/

b

0.6 mA

70

m

A/

b

0.65 mA

b

3 mA/24 mA (20 mA)

b

1 mA/20 mA

Q

0

, Q

7

Functional Description

The ’F299 contains eight edge-triggered D-type flip-flops

and the interstage logic necessary to perform synchronous

shift left, shift right, parallel load and hold operations. The

type of operation is determined by S

0

and S

1

, as shown in

the Mode Select Table. All flip-flop outputs are brought out

through TRI-STATE buffers to separate I/O pins that also

serve as data inputs in the parallel load mode. Q

0

and Q

7

are also brought out on other pins for expansion in serial

shifting of longer words.

A LOW signal on MR overrides the Select and CP inputs

and resets the flip-flops. All other state changes are initiated

by the rising edge of the clock. Inputs can change when the

clock is in either state provided only that the recommended

setup and hold times, relative to the rising edge of CP, are

observed.

A HIGH signal on either OE

1

or OE

2

disables the TRI-

STATE buffers and puts the I/O pins in the high impedance

state. In this condition the shift, hold, load and reset opera-

tions can still occur. The TRI-STATE outputs are also dis-

abled by HIGH signals on both S

0

and S

1

in preparation for

a parallel load operation.

Mode Select Table

Inputs

Response

MR S

1

S

0

CP

L

H

H

H

H

X

H

L

H

L

X

H

L

Parallel Load; I/O

Q

n

H

L

Shift Right; DS

0

x

Q

0

, Q

0

x

Q

1

, etc.

L

L

Shift Left; DS

7

x

Q

7

, Q

7

x

Q

6

, etc.

L

X

Hold

X

Asynchronous Reset; Q

0

–Q

7

e

LOW

H

e

HIGH Voltage Level

L

e

LOW Voltage Level

X

e

Immaterial

L

e

LOW-to-HIGH Clock Transition

2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74F299SJ | Octal Universal Shift/Storage Register with Common Parallel I/O Pins |

| 74F299PC | Octal Universal Shift/Storage Register with Common Parallel I/O Pins |

| 74F299SC | Octal Universal Shift/Storage Register with Common Parallel I/O Pins |

| 74F299SJ | CABLE MARKER, A REEL 2.4M |

| 74F299 | Octal Universal Shift/Storage Register with Common Parallel I/O Pins |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74F299SCX | 功能描述:計(jì)數(shù)器移位寄存器 Oct Univ Shf/Sto Reg RoHS:否 制造商:Texas Instruments 計(jì)數(shù)器類型: 計(jì)數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時(shí)間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| 74F299SJ | 功能描述:計(jì)數(shù)器移位寄存器 Oct Univ Shf/Sto Reg RoHS:否 制造商:Texas Instruments 計(jì)數(shù)器類型: 計(jì)數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時(shí)間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| 74F299SJX | 功能描述:計(jì)數(shù)器移位寄存器 Oct Univ Shf/Sto Reg RoHS:否 制造商:Texas Instruments 計(jì)數(shù)器類型: 計(jì)數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時(shí)間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| 74F30 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:8-input NAND gate |

| 74F30_04 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:8-Input NAND Gate |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。