- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370124 > 74F193SJ (FAIRCHILD SEMICONDUCTOR CORP) Up/Down Binary Counter with Separate Up/Down Clocks PDF資料下載

參數(shù)資料

| 型號(hào): | 74F193SJ |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 通用總線功能 |

| 英文描述: | Up/Down Binary Counter with Separate Up/Down Clocks |

| 中文描述: | F/FAST SERIES, SYN POSITIVE EDGE TRIGGERED 4-BIT BIDIRECTIONAL BINARY COUNTER, PDSO16 |

| 封裝: | 5.30 MM, EIAJ TYPE2, SOP-16 |

| 文件頁(yè)數(shù): | 2/10頁(yè) |

| 文件大小: | 191K |

| 代理商: | 74F193SJ |

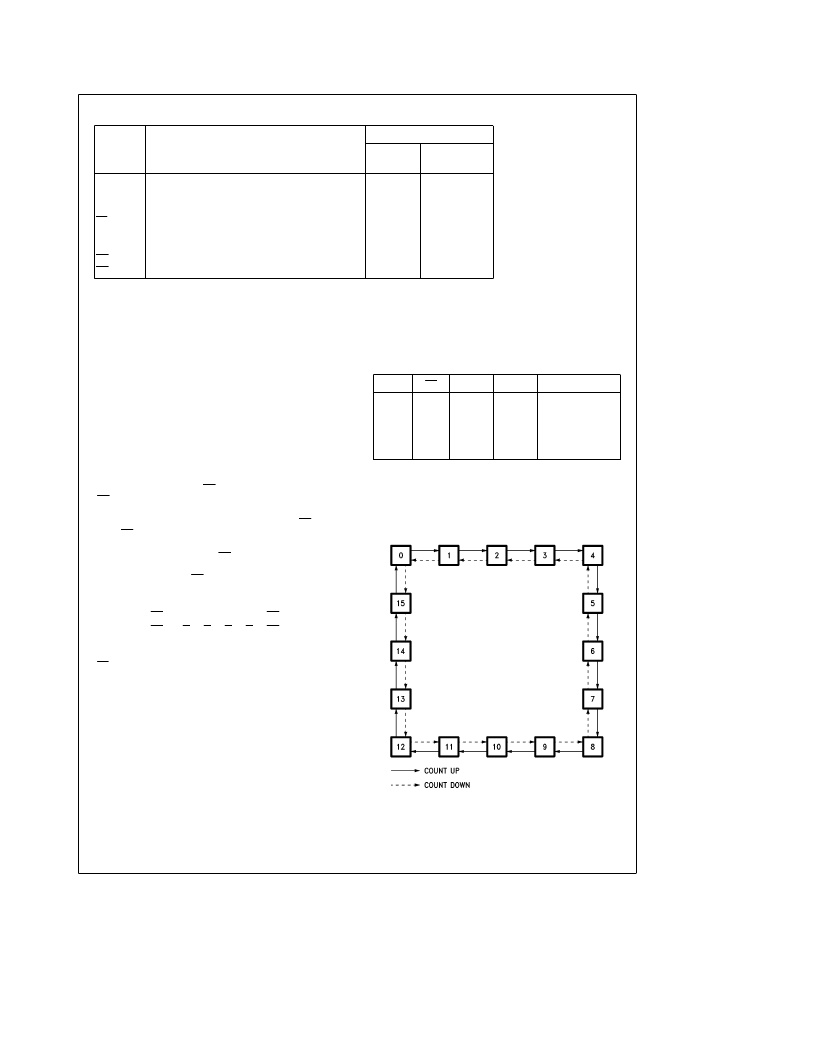

Unit Loading/Fan Out

54F/74F

Pin Names

Description

U.L.

Input I

IH

/I

IL

HIGH/LOW Output I

OH

/I

OL

CP

U

CP

D

MR

PL

P

0

–P

3

Q

0

–Q

3

TC

D

TC

U

Count Up Clock Input (Active Rising Edge)

Count Down Clock Input (Active Rising Edge)

Asynchronous Master Reset Input (Active HIGH)

Asynchronous Parallel Load Input (Active LOW)

Parallel Data Inputs

Flip-Flop Outputs

Terminal Count Down (Borrow) Output (Active LOW)

Terminal Count Up (Carry) Output (Active LOW)

1.0/3.0

1.0/3.0

1.0/1.0

1.0/1.0

1.0/1.0

50/33.3

50/33.3

50/33.3

20

m

A/

b

1.8 mA

20

m

A/

b

1.8 mA

20

m

A/

b

0.6 mA

20

m

A/

b

0.6 mA

20

m

A/

b

0.6 mA

b

1 mA/20 mA

b

1 mA/20 mA

b

1 mA/20 mA

Functional Description

The ’F193 is a 4-bit binary synchronous up/down (revers-

ible) counter. It contains four edge-triggered flip-flops, with

internal gating and steering logic to provide master reset,

individual preset, count up and count down operations.

A LOW-to-HIGH transition on the CP input to each flip-flop

causes the output to change state. Synchronous switching,

as opposed to ripple counting, is achieved by driving the

steering gates of all stages from a common Count Up line

and a common Count Down line, thereby causing all state

changes to be initiated simultaneously. A LOW-to-HIGH

transition on the Count Up input will advance the count by

one; a similar transition on the Count Down input will de-

crease the count by one. While counting with one clock in-

put, the other should be held HIGH, as indicated in the

Function Table.

The Terminal Count Up (TC

U

) and Terminal Count Down

(TC

D

) outputs are normally HIGH. When the circuit has

reached the maximum count state 15, the next HIGH-to-

LOW transition of the Count Up Clock will cause TC

U

to go

LOW. TC

U

will stay LOW until CP

U

goes HIGH again, thus

effectively repeating the Count Up Clock, but delayed by

two gate delays. Similarly, the TC

D

output will go LOW when

the circuit is in the zero state and the Count Down Clock

goes LOW. Since the TC outputs repeat the clock wave-

forms, they can be used as the clock input signals to the

next higher order circuit in a multistage counter.

TC

U

e

Q

0

#

Q

1

#

Q

2

#

Q

3

#

CP

U

TC

D

e

Q

0

#

Q

1

#

Q

2

#

Q

3

#

CP

D

The ’F193 has an asynchronous parallel load capability per-

mitting the counter to be preset. When the Parallel Load

(PL) and the Master Reset (MR) inputs are LOW, informa-

tion present on the Parallel Data input (P

0

–P

3

) is loaded

into the counter and appears on the outputs regardless of

the conditions of the clock inputs. A HIGH signal on the

Master Reset input will disable the preset gates, override

both clock inputs, and latch each Q output in the LOW state.

If one of the clock inputs is LOW during and after a reset or

load operation, the next LOW-to-HIGH transition of that

clock will be interpreted as a legitimate signal and will be

counted.

Function Table

MR

PL

CP

U

CP

D

Mode

H

L

L

L

L

X

L

H

H

H

X

X

H

X

X

H

H

Reset (Asyn.)

Preset (Asyn.)

No Change

Count Up

Count Down

L

H

L

H

e

HIGH Voltage Level

L

e

LOW Voltage Level

X

e

Immaterial

L

e

LOW-to-HIGH Clock Transition

State Diagram

TL/F/9497–5

2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74F193SC | Up/Down Binary Counter with Separate Up/Down Clocks |

| 74F193PC | Up/Down Binary Counter with Separate Up/Down Clocks |

| 74F243LMX | Quad Bus Transceiver with TRI-STATE Outputs |

| 74F243SC | Quad Bus Transceiver with TRI-STATE Outputs |

| 74F243SCQB | Quad Bus Transceiver with TRI-STATE Outputs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74F193SJ_Q | 功能描述:計(jì)數(shù)器 IC Up/Down Binary Ctr RoHS:否 制造商:NXP Semiconductors 計(jì)數(shù)器類型:Binary Counters 邏輯系列:74LV 位數(shù):10 計(jì)數(shù)法: 計(jì)數(shù)順序: 工作電源電壓:1 V to 5.5 V 工作溫度范圍:- 40 C to + 125 C 封裝 / 箱體:SOT-109 封裝:Reel |

| 74F193SJX | 功能描述:計(jì)數(shù)器移位寄存器 Up/Dn Binary Counter Clear Square Base RoHS:否 制造商:Texas Instruments 計(jì)數(shù)器類型: 計(jì)數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時(shí)間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| 74F194 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:4-Bit Bidirectional Universal Shift Register |

| 74F194_04 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:4-Bit Bidirectional Universal Shift Register |

| 74F194DC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。