- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄68813 > 73S8024RN-32IM (MAXIM INTEGRATED PRODUCTS INC) SPECIALTY ANALOG CIRCUIT, QCC32 PDF資料下載

參數(shù)資料

| 型號: | 73S8024RN-32IM |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | 模擬信號調(diào)理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, QCC32 |

| 封裝: | QFN-32 |

| 文件頁數(shù): | 2/23頁 |

| 文件大小: | 318K |

| 代理商: | 73S8024RN-32IM |

73S8024RN

Low Cost Smart Card Interface

DATA SHEET

Page: 10 of 23

2005 TERIDIAN Semiconductor Corporation

Rev 1.5

OFF AND FAULT DETECTION

There are two different cases that the system controller can monitor the

OFF signal: to query regarding the card

presence outside card sessions, or for fault detection during card sessions.

Outside a card session: In this condition,

CMDVCC is always high, OFF is low if the card is not present, and high

if the card is present. Because it is outside a card session, any fault detection will not act upon the

OFF signal. No

deactivation is required during this time.

During a card session:

CMDVCC is always low, and OFF falls low if the card is extracted or if any fault detection

is detected. At the same time that

OFF is set low, the sequencer starts the deactivation process.

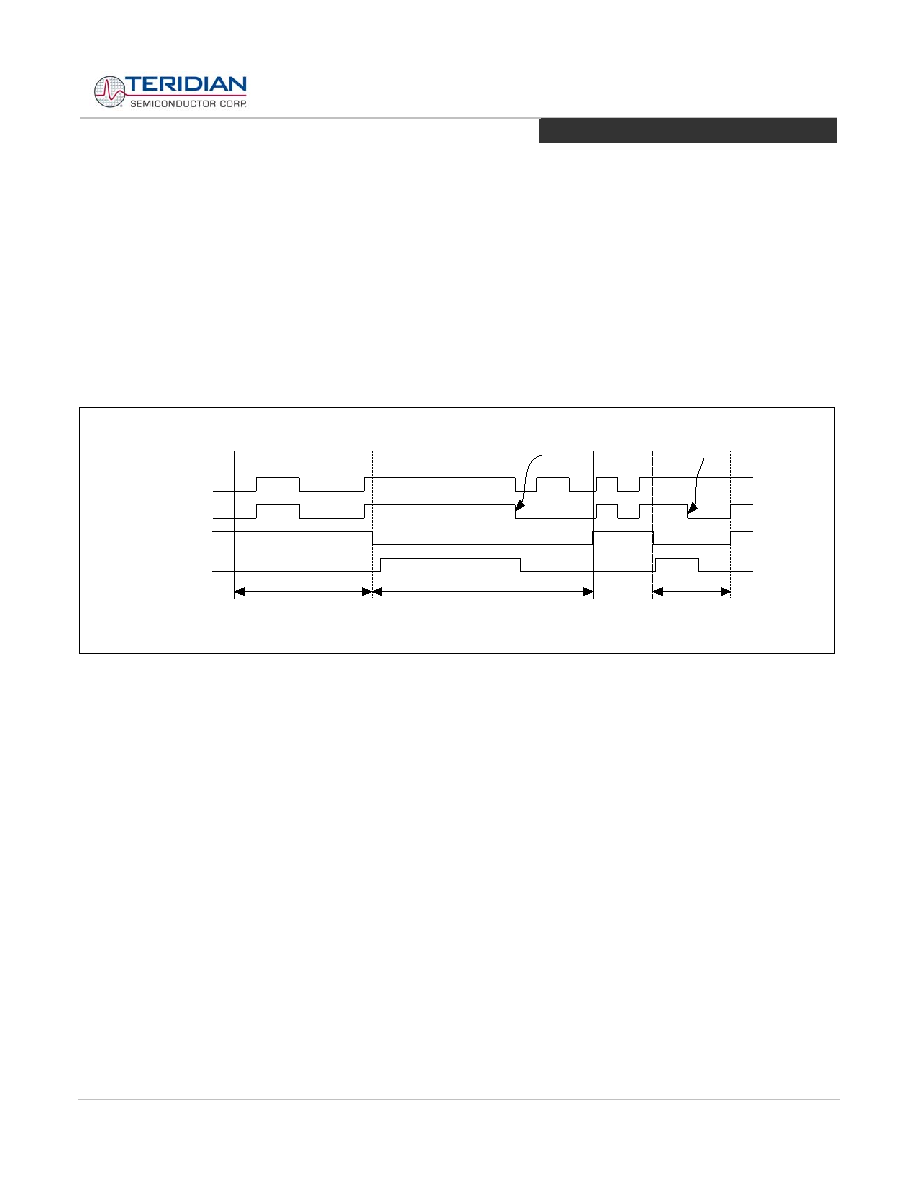

The Figure 5 shows the timing diagram for the signals

CMDVCC, PRES, and OFF during a card session and

outside the card session:

PRES

OFF

CMDVCC

VCC

outside card session

within card session

OFFis lowby

card extracted

OFFis lowby

anyfault

within card

session

Figure 5: Timing Diagram - Management of the Interrupt Line

OFF

I/O CIRCUITRY AND TIMING

The states of the I/O, AUX1, and AUX2 pins are low after power on reset and they are in high when the activation

sequencer turns on the I/O reception state. See Activation Sequence timing section for more details on when the

I/O reception is enabled. The states of I/OUC, AUX1UC, and AUX2UC are high after power on reset.

Within a card session and when the I/O reception state is turn on, the first I/O line on which a falling edge is

detected becomes the input I/O line and the other becomes the output I/O line. When the input I/O line rising edge

is detected then both I/O lines return to their neutral state.

The Figure 6 shows the state diagram of how the I/O and I/OUC lines are managed to become input or output.

The delay between the I/O signals is shown in Figure 7.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 73S8024RN-ILR | SPECIALTY ANALOG CIRCUIT, PDSO28 |

| 73S8024RN-20IM | SPECIALTY ANALOG CIRCUIT, QCC20 |

| 73S8024RN-ILR | SPECIALTY ANALOG CIRCUIT, PDSO28 |

| 73S8024RN-20IMR | SPECIALTY ANALOG CIRCUIT, QCC20 |

| 73S8024RN-32IMR | SPECIALTY ANALOG CIRCUIT, QCC32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 73S8024RN-32IM/F | 功能描述:IC SMART CARD INTERFACE 32-QFN RoHS:是 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| 73S8024RN-32IMR/F | 功能描述:IC SMART CARD INTERFACE 32-QFN RoHS:是 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| 73S8024RN-DB | 功能描述:界面開發(fā)工具 73S8024RN Demo Brd RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| 73S8024RN-IL | 制造商:TERIDIAN 功能描述: 制造商:TDK 功能描述:SPECIALTY ANALOG CIRCUIT, 28 Pin Plastic SMT |

| 73S8024RN-IL/F | 功能描述:輸入/輸出控制器接口集成電路 Smart Card Interface ISO7816-3 & EVM4.0 RoHS:否 制造商:Silicon Labs 產(chǎn)品: 輸入/輸出端數(shù)量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。