- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄68811 > 71M6531D-IMR/F (TERIDIAN SEMICONDUCTOR CORP) 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, QCC68 PDF資料下載

參數(shù)資料

| 型號(hào): | 71M6531D-IMR/F |

| 廠商: | TERIDIAN SEMICONDUCTOR CORP |

| 元件分類(lèi): | 電源管理 |

| 英文描述: | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, QCC68 |

| 封裝: | LEAD FREE, QFN-68 |

| 文件頁(yè)數(shù): | 106/120頁(yè) |

| 文件大小: | 2477K |

| 代理商: | 71M6531D-IMR/F |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)當(dāng)前第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)

Data Sheet 71M6531D/F-71M6532D/F

FDS 6531/6532 005

86

2005-2010 TERIDIAN Semiconductor Corporation

v1.3

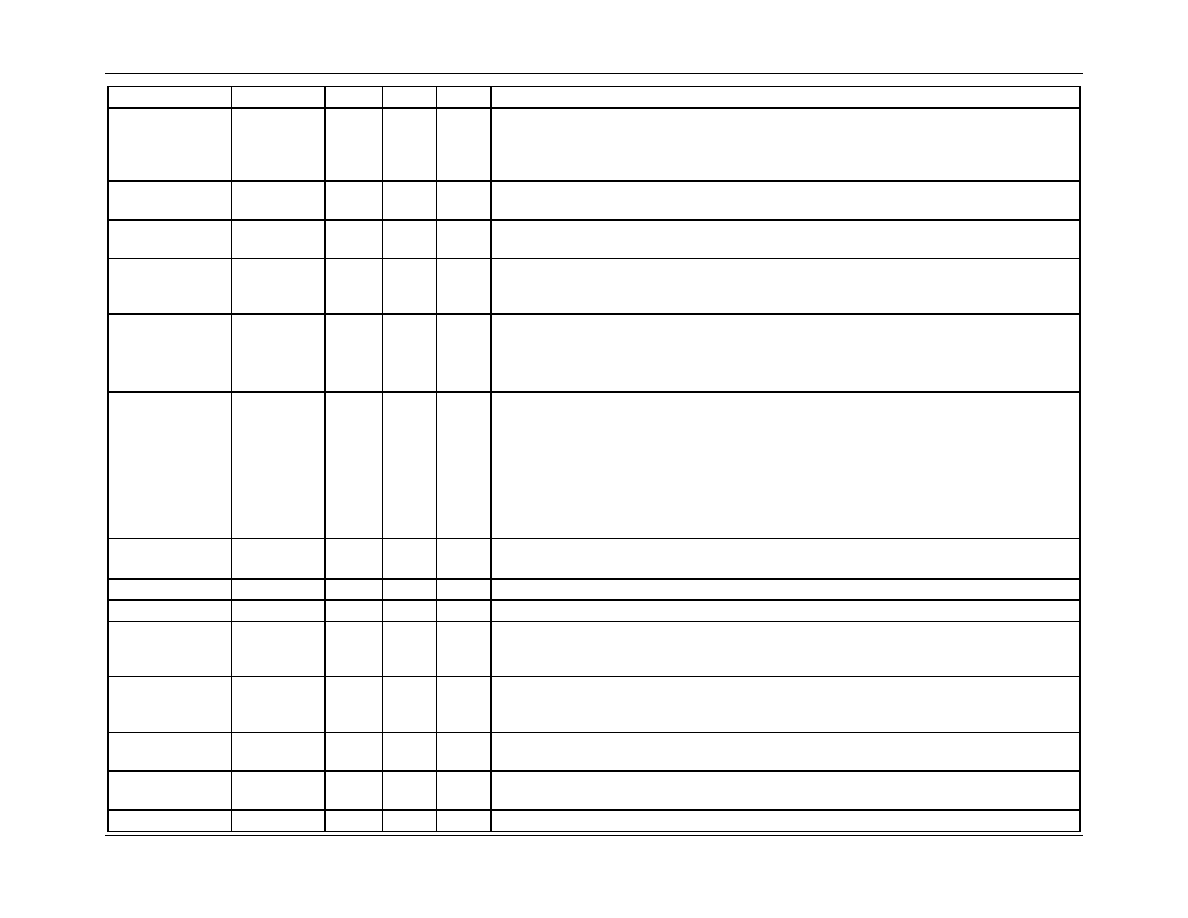

Name

Location

Reset

Wake

Dir

Description

SECURE

SFRB2[6]

0

–

R/W

When set, enables security provisions that prevent external reading of the flash memory

(zeros will be returned if the flash is read). SECURE should be set during the preboot

phase, i.e. while PREBOOT is set. SECURE is cleared when the flash is mass-erased

and when the chip is reset. The bit may only be set, attempts to write zero are ignored.

SEL_IAN

20AC[1]

0

R/W

When set to 1, selects differential mode for the current input (IAP, IAN). When 0, the

input remains single-ended (71M6532D/F only).

SEL_IBN

20AC[5]

0

R/W

When set to 1, selects differential mode for the current input (IBP, IBN). When 0, the

input remains single-ended (71M6532D/F only).

SLEEP

20A9[6]

0

W

Puts the 71M6531 into SLEEP mode. This bit is ignored if system power is present.

The 71M6531 will wake when the autowake timer times out, when the push button is

pushed, when system power returns, or when RESET goes high.

SLOT0_SEL[3:0]

SLOT1_SEL[3:0]

SLOT2_SEL[3:0]

SLOT3_SEL[3:0]

2090[3:0]

2090[7:4]

2091[3:0]

2091[7:4]

0

1

2

3

0

1

2

3

R/W

Primary multiplexer frame analog input selection. These bits map the selected input,

0-3 to the multiplexer state. The ADC output is always written to the memory location

corresponding to the input, regardless of which multiplexer state an input is mapped to

(see Section 1.2 Analog Front End (AFE)).

SLOT0_ALTSEL

[3:0]

SLOT1_ALTSEL

[3:0]

SLOT2_ALTSEL

[3:0]

SLOT3_ALTSEL

[3:0]

2096[3:0]

2096[7:4]

2097[3:0]

2097[7:4]

A

1

2

3

A

1

B

3

R/W

Alternate multiplexer frame analog input selection. Maps the selected input to the

multiplexer state.

The additional inputs, 10 and 11 in the alternate frame are:

10 = TEMP

11 = VBAT

SP_ADDR[15:8]

SP_ADDR[7:0]

2072[7:0]

2073[7:0]

0

R

SPI Address. 16-bit address from the bus master.

SP_CMD

2071

0

R

SPI command. 8-bit command from the bus master.

SPE

2070[7]

0

R/W

SPI port enable. Enables the SPI interface on pins SEG3 through SEG5.

SPI_FLAG

20B1[4]

1

R/W

SPI interrupt flag. The flag is set by the hardware and is cleared by the firmware writing

a 0. Firmware using this interrupt should clear the spurious interrupt indication during

initialization.

SUBSEC[7:0]

2014[7:0]

–

R

The remaining count, in terms of 1/256 RTC cycles, to the next one second boundary.

SUBSEC may be read by the MPU after the one second interrupt and before reaching

the next one second boundary. Setting RST_SUBSEC will clear SUBSEC.

SUM_CYCLES

[5:0]

2001[5:0]

0

R/W

The number of pre-summer outputs summed in the final summing stage of the CE.

TMUX[4:0]

20AA[4:0]

2

–

R/W

Selects one of 32 signals for TMUXOUT. For details, see Section 1.5.17 Test Ports

TRIM[7:0]

20FF

0

R/W

Contains fuse information, depending on the value written to TRIMSEL[3:0].

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 71M6532D-IGTR/F | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PQFP100 |

| 71M6532F-IGT/F | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PQFP100 |

| 71M6531D-IM/F | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, QCC68 |

| 71M6531F-IMR/F | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, QCC68 |

| 71M6531F-IM/F | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, QCC68 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 71M6531F | 制造商:TERIDIAN 制造商全稱(chēng):TERIDIAN 功能描述:Energy Meter IC |

| 71M6531F-DB | 功能描述:開(kāi)發(fā)板和工具包 - 8051 71M6531F Demo Brd RoHS:否 制造商:Silicon Labs 產(chǎn)品:Development Kits 工具用于評(píng)估:C8051F960, Si7005 核心: 接口類(lèi)型:USB 工作電源電壓: |

| 71M6531F-IM/F | 功能描述:計(jì)量片上系統(tǒng) - SoC Residential Energy Meter IC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 處理器系列:71M6511 類(lèi)型:Metering SoC 最大時(shí)鐘頻率:70 Hz 程序存儲(chǔ)器大小:64 KB 數(shù)據(jù) RAM 大小:7 KB 接口類(lèi)型:UART 可編程輸入/輸出端數(shù)量:12 片上 ADC: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:LQFP-64 封裝:Reel |

| 71M6531F-IM/F3 | 功能描述:計(jì)量片上系統(tǒng) - SoC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 處理器系列:71M6511 類(lèi)型:Metering SoC 最大時(shí)鐘頻率:70 Hz 程序存儲(chǔ)器大小:64 KB 數(shù)據(jù) RAM 大小:7 KB 接口類(lèi)型:UART 可編程輸入/輸出端數(shù)量:12 片上 ADC: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:LQFP-64 封裝:Reel |

| 71M6531F-IM/F4 | 功能描述:計(jì)量片上系統(tǒng) - SoC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 處理器系列:71M6511 類(lèi)型:Metering SoC 最大時(shí)鐘頻率:70 Hz 程序存儲(chǔ)器大小:64 KB 數(shù)據(jù) RAM 大小:7 KB 接口類(lèi)型:UART 可編程輸入/輸出端數(shù)量:12 片上 ADC: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:LQFP-64 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。