- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄68810 > 71M6521DE-IGTR/F (MAXIM INTEGRATED PRODUCTS INC) SPECIALTY ANALOG CIRCUIT, QFP64 PDF資料下載

參數(shù)資料

| 型號(hào): | 71M6521DE-IGTR/F |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類(lèi): | 模擬信號(hào)調(diào)理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, QFP64 |

| 封裝: | LEAD FREE, LQFP-64 |

| 文件頁(yè)數(shù): | 43/103頁(yè) |

| 文件大小: | 1691K |

| 代理商: | 71M6521DE-IGTR/F |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)當(dāng)前第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)

71M6521DE/71M6521FE

Energy Meter IC

DATA SHEET

OCTOBER 2010

Page: 44 of 103

2005-2010 Teridian Semiconductor Corporation

v1.1

A Maxim Integrated Products Brand

19-5370; 10/10

Three-Wire EEPROM Interface

A 500kHz three-wire interface, using SDATA, SCK, and a DIO pin for CS is available. The interface is selected with

DIO_EEX=3. The same 2-wire EECTRL register is used, except the bits are reconfigured, as shown in Table 58. When EECTRL

is written, up to 8 bits from EEDATA are either written to the EEPROM or read from the EEPROM, depending on the values of

the EECTRL bits.

Control

Bit

Name

Read/Write

Description

7

WFR

W

Wait for Ready. If this bit is set, the trailing edge of BUSY will be delayed

until a rising edge is seen on the data line. This bit can be used during

the last byte of a Write command to cause the INT5 interrupt to occur

when the EEPROM has finished its internal write sequence. This bit is

ignored if HiZ=0.

6

BUSY

R

Asserted while serial data bus is busy. When the BUSY bit falls, an INT5

interrupt occurs.

5

HiZ

W

Indicates that the SD signal is to be floated to high impedance immedi-

ately after the last SCK rising edge.

4

RD

W

Indicates that EEDATA is to be filled with data from EEPROM.

3-0

CNT[3:0]

W

Specifies the number of clocks to be issued. Allowed values are 0

through 8. If RD=1, CNT bits of data will be read MSB first, and right

justified into the low order bits of EEDATA. If RD=0, CNT bits will be sent

MSB first to EEPROM, shifted out of EEDATA’s MSB. If CNT is zero,

SDATA will simply obey the HiZ bit.

Table 58: EECTRL bits for 3-wire interface

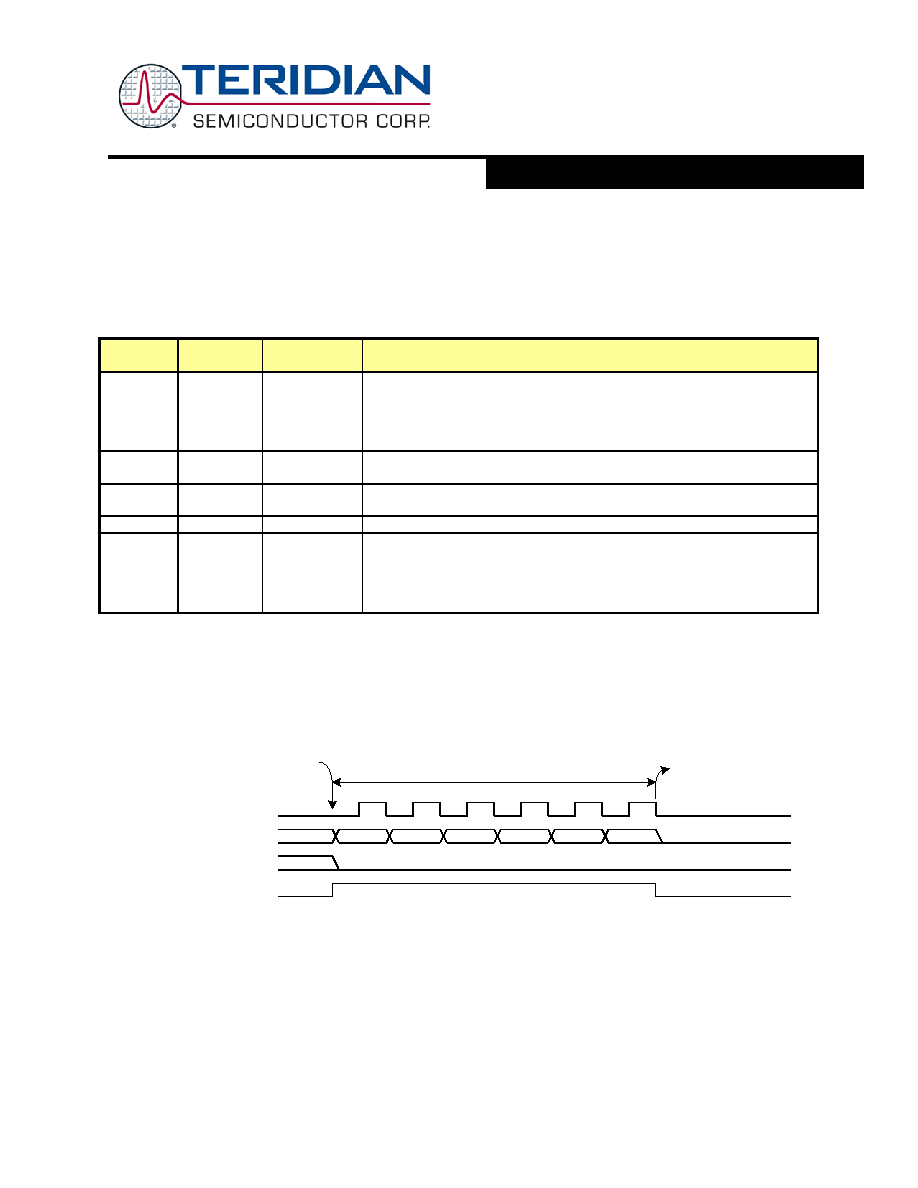

The timing diagrams in Figure 9 through Figure 13 describe the 3-wire EEPROM interface behavior. All commands begin when

the EECTRL register is written. Transactions start by first raising the DIO pin that is connected to CS. Multiple 8-bit or less

commands such as those shown in Figure 9 through Figure 13 are then sent via EECTRL and EEDATA. When the transaction

is finished, CS must be lowered. At the end of a Read transaction, the EEPROM will be driving SDATA, but will transition to

HiZ (high impedance) when CS falls. The firmware should then immediately issue a write command with CNT=0 and HiZ=0 to

take control of SDATA and force it to a low-Z state.

SCLK (output)

BUSY (bit)

CNT Cycles (6 shown)

SDATA (output)

Write -- No HiZ

D2

D3

D4

D5

D6

D7

EECTRL Byte Written

INT5

SDATA output Z

(LoZ)

Figure 9: 3-Wire Interface. Write Command, HiZ=0.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 71M6521DE-IM/F | SPECIALTY ANALOG CIRCUIT, QCC68 |

| 71M6521FE-IMR/F | SPECIALTY ANALOG CIRCUIT, QCC68 |

| 71M6521DE-IGT/F | SPECIALTY ANALOG CIRCUIT, QFP64 |

| 71M6521FE-IGTR/F | SPECIALTY ANALOG CIRCUIT, QFP64 |

| 71M6521DE-IMR/F | SPECIALTY ANALOG CIRCUIT, QCC68 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 71M6521DE-IM/F | 功能描述:計(jì)量片上系統(tǒng) - SoC Residential Energy Meter IC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 處理器系列:71M6511 類(lèi)型:Metering SoC 最大時(shí)鐘頻率:70 Hz 程序存儲(chǔ)器大小:64 KB 數(shù)據(jù) RAM 大小:7 KB 接口類(lèi)型:UART 可編程輸入/輸出端數(shù)量:12 片上 ADC: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:LQFP-64 封裝:Reel |

| 71M6521DEIM-DB | 制造商:Maxim Integrated Products 功能描述:Development Boards & Kits - 8051 71M6521DE Demo Brd |

| 71M6521DE-IMR/F | 功能描述:計(jì)量片上系統(tǒng) - SoC Residential Energy Meter IC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 處理器系列:71M6511 類(lèi)型:Metering SoC 最大時(shí)鐘頻率:70 Hz 程序存儲(chǔ)器大小:64 KB 數(shù)據(jù) RAM 大小:7 KB 接口類(lèi)型:UART 可編程輸入/輸出端數(shù)量:12 片上 ADC: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:LQFP-64 封裝:Reel |

| 71M6521DH | 制造商:MAXIM 制造商全稱(chēng):Maxim Integrated Products 功能描述:Energy Meter ICs |

| 71M6521DH-IGT/F | 制造商:MAXIM 制造商全稱(chēng):Maxim Integrated Products 功能描述:Energy Meter ICs |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。