- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄68810 > 7106L-D40-T (UNISONIC TECHNOLOGIES CO LTD) 1-CH PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDIP40 PDF資料下載

參數(shù)資料

| 型號: | 7106L-D40-T |

| 廠商: | UNISONIC TECHNOLOGIES CO LTD |

| 元件分類: | ADC |

| 英文描述: | 1-CH PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDIP40 |

| 封裝: | LEAD FREE, DIP-40 |

| 文件頁數(shù): | 4/18頁 |

| 文件大小: | 438K |

| 代理商: | 7106L-D40-T |

7106

CMOS IC

UNISONICTECHNOLOGIESCO.,LTD

12 of 18

www.unisonic.com.tw

QW-R502-018.D

DETAILED DESCRIPTION(Cont.)

SYSTEM TIMING

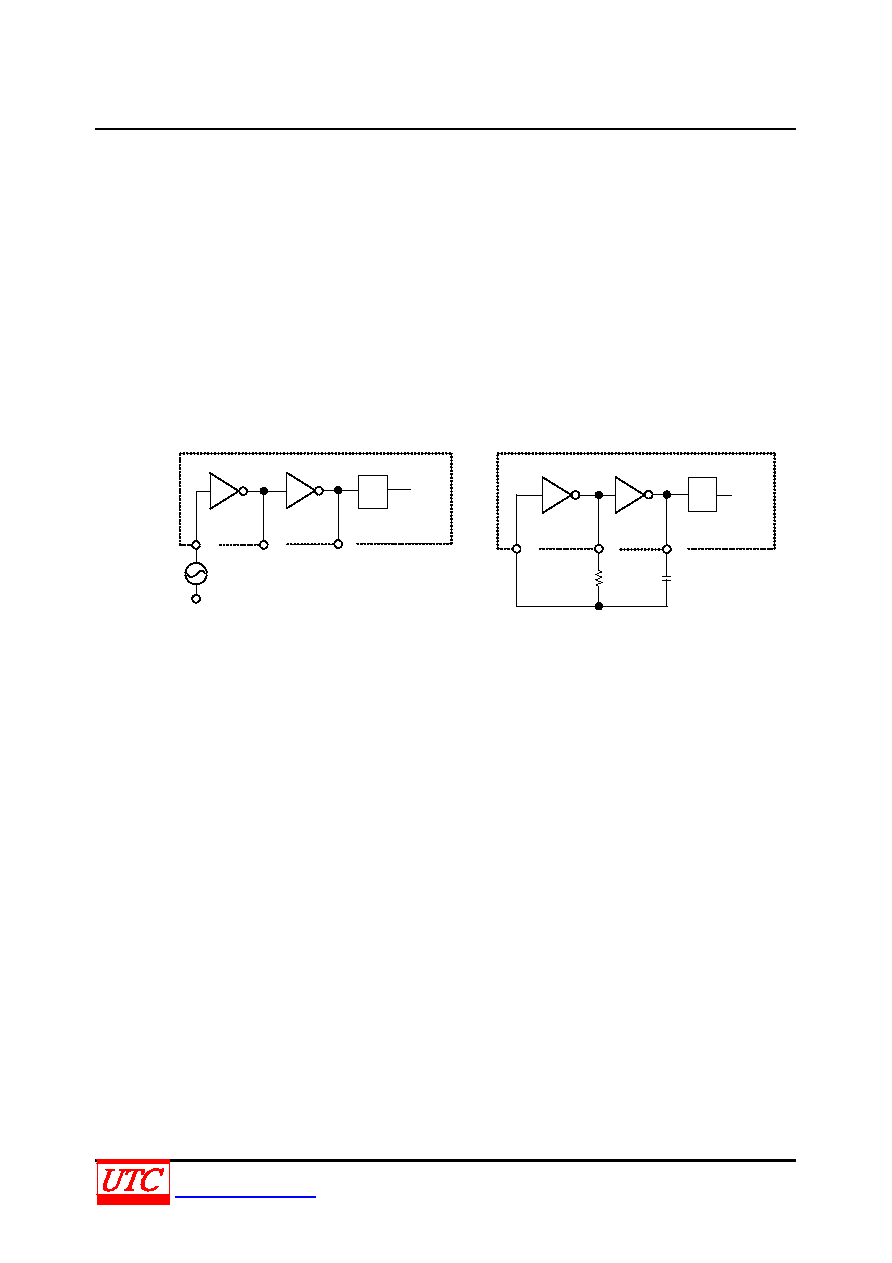

Figure 6 shows the clocking arrangement used in the UTC 7106. Two basic clocking arrangements can be used:

1. Figure 6A. An external oscillator connected to pin 40.

2. Figure 6B. An R-C oscillator using all three pins.

The oscillator frequency is divided by four before it clocks the decade counters. It is then further divided to form

the three convert-cycle phases. These are signal integrate (1000 counts), reference de-integrate (0 to 2000 counts)

and auto-zero(1000 ~ 3000 counts). For signals less than full scale. auto-zero gets the unused portion of reference

de-integrate. This makes a complete measure cycle of 4,000 counts (16,000 clock pulses) independent of input

voltage. For three readings/second, an oscillator frequency of 48kHz would be used.

To achieve maximum rejection of 60Hz pickup, the signal integrate cycle should be a multiple of 60Hz. Oscillator

frequencies of 240kHz, 120kHz, 80kHz, 60kHz, 48kHz, 40kHz, 33 1/3kHz, etc. should be selected. For 50Hz

rejection, Oscillator frequencies of 200kHz, 100kHz, 66 2/3kHz, 50kHz, 40kHz, etc. would be suitable. Note that

40kHz (2.5 readings/second) will reject both 50Hz and 60Hz (also 400Hz and 440Hz).

40

39

38

TEST

CLOCK

INTERNAL TO PART

FIGURE 6A

40

39

38

RC OSCILLATOR

CLOCK

INTERNAL TO PART

FIGURE 6B

R

C

Figure 6. Clock Circuits

÷ 4

COMPONENT VALUE SELECTION

Integrating Resistor

Both the buffer amplifier and the integrator have a class A output stage with 100μA of quiescent current. They can

supply 4μA of drive current with negligible nonlinearity. The integrating resistor should be large enough to remain in

this very linear region over the input voltage range, but small enough that undue leakage requirements are not

placed on the PC board. For 2V full scale, 470k is near optimum and similarly a 47k for a 200mV scale.

Integrating Capacitor

The integrating capacitor should be selected to give the maximum voltage swing that ensures tolerance buildup

will not saturate the integrator swing(approximately. 0.3V from either supply).In the UTC 7106, when the analog

COMMON is used as a reference, a nominaul+2V full scale integrator swing is fine. For three readings/second

(48kHz clock) nominal values for CINT are 0.22μF and 0.10μF, respectively. Of course, if different oscillator

frequencies are used, these values should be changed in inverse proportion to maintain the same output swing.

An additional requirement of the integrating capacitor is that it must have a low dielectric absorption to prevent

roll-over errors. While other types of capacitors are adequate for this application, polypropylene capacitors give

undetectable errors at reasonable cost.

Auto-Zero Capacitor

The size of the auto-zero capacitor has some influence on the noise of the system. For 200mV full scale where

noise is very important, a 0.47μF capacitor is recommended. On the 2V scale, a 0.047μF capacitor increases the

speed of recovery from overload and is adequate for noise on this scale.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 7106L-R40-T | 1-CH PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO40 |

| 7106G-D40-T | 1-CH PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDIP40 |

| 7106L-R40-R | 1-CH PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO40 |

| 7106L-QM1-Y | 1-CH PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP44 |

| 7106G-R40-T | 1-CH PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 7106L-QM1-Y | 制造商:UTC-IC 制造商全稱:UTC-IC 功能描述:3 ? DIGIT, LCD DISPLAY, A/D CONVERTERS |

| 7106L-R40-R | 制造商:UTC-IC 制造商全稱:UTC-IC 功能描述:3 ? DIGIT, LCD DISPLAY, A/D CONVERTERS |

| 7106L-R40-T | 制造商:UTC-IC 制造商全稱:UTC-IC 功能描述:3 ? DIGIT, LCD DISPLAY, A/D CONVERTERS |

| 7106MQ | 制造商:Apex Tool Group 功能描述:HANDLE,WORK STA,7190 |

| 7106PD | 制造商:Aavid Thermalloy 功能描述:- Bulk 制造商:Aavid Thermalloy 功能描述:Heat Sink Passive D2 PAK/TO-263/SO-10/MO-184 Surface Mount 15?C/W Pre Tin |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。