- 您現(xiàn)在的位置:買賣IC網 > PDF目錄294088 > 70V34S20PFGI (INTEGRATED DEVICE TECHNOLOGY INC) 4K X 18 DUAL-PORT SRAM, 20 ns, PQFP100 PDF資料下載

參數資料

| 型號: | 70V34S20PFGI |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | SRAM |

| 英文描述: | 4K X 18 DUAL-PORT SRAM, 20 ns, PQFP100 |

| 封裝: | 14 X 14 MM, 1.40 MM HEIGHT, GREEN, PLASTIC, TQFP-100 |

| 文件頁數: | 15/25頁 |

| 文件大?。?/td> | 211K |

| 代理商: | 70V34S20PFGI |

6.42

IDT70V35/34S/L

(IDT70V25/24S/L)

High-Speed 3.3V 8/4K x 18 (8/4K x 16) Dual-Port Static RAM

Industrial and Commercial Temperature Ranges

22

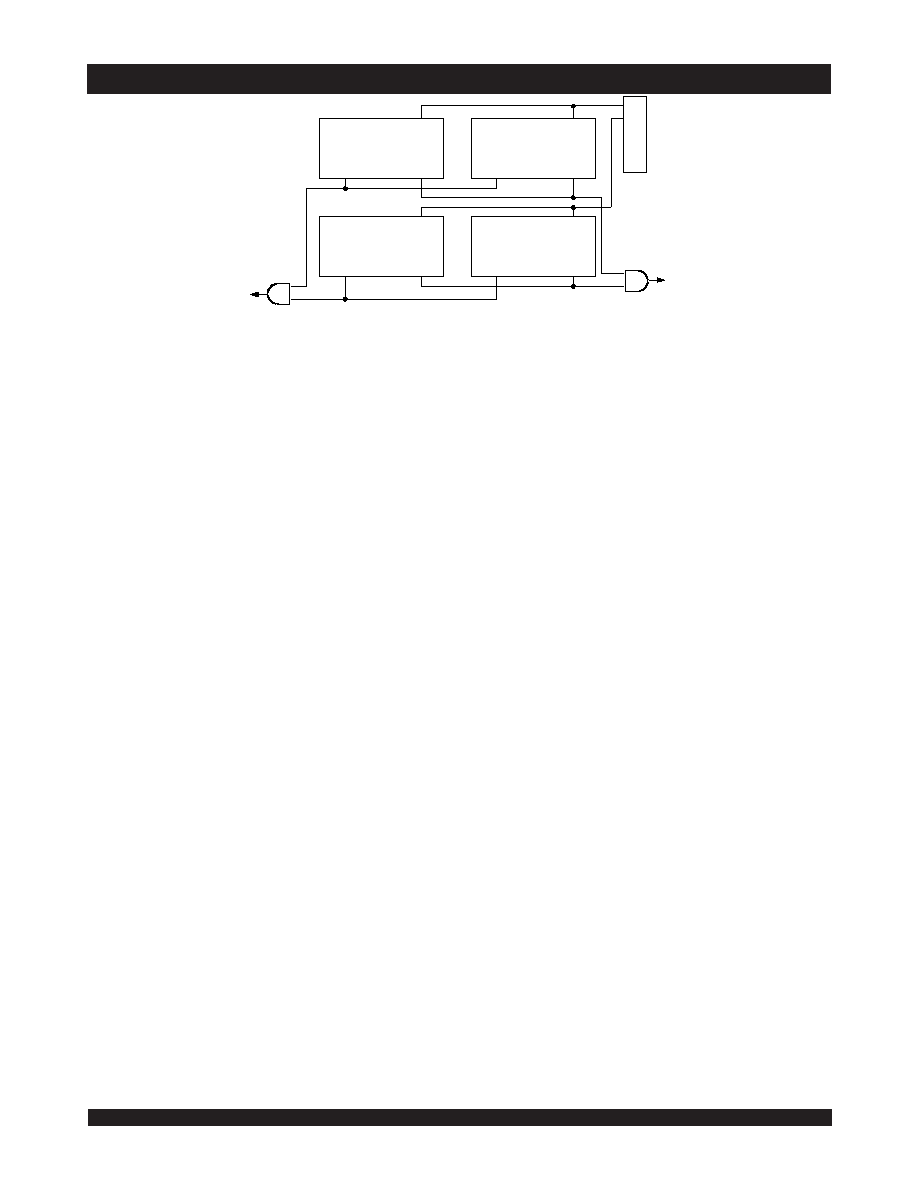

Figure 3. Busy and chip enable routing for both width and depth expansion with IDT70V35/34 (IDT70V25/24) SRAMs.

not desirable, the

BUSYlogiccanbedisabledbyplacingthepartinslave

mode with the M/

Spin.OnceinslavemodetheBUSYpinoperatessolely

as a write inhibit input pin. Normal operation can be programmed by tying

the

BUSY pins HIGH. If desired, unintended write operations can be

prevented to a port by tying the

BUSY pin for that port LOW.

The

BUSY outputs on the IDT70V35/34 (IDT70V25/24) SRAM in

master mode, are push-pull type outputs and do not require pull up

resistors to operate. If these SRAMs are being expanded in depth, then

the

BUSYindicationfortheresultingarrayrequirestheuseofanexternal

AND gate.

Width Expansion with Busy Logic

Master/Slave Arrays

When expanding an IDT70V35/34 (IDT70V25/24) SRAM array in

widthwhileusing

BUSYlogic,onemasterpartisusedtodecidewhichside

of the SRAM array will receive a

BUSY indication, and to output that

indication. Any number of slaves to be addressed in the same address

range as the master, use the

BUSY signal as a write inhibit signal. Thus

on the IDT70V35/34 (IDT70V25/24) SRAM the

BUSY pin is an output if

the part is used as a master (M/

Spin = VIH), andthe BUSYpinisaninput

if the part used as a slave (M/

S pin = VIL) as shown in Figure 3.

Iftwoormoremasterpartswereusedwhenexpandinginwidth,asplit

decision could result with one master indicating

BUSYononesideofthe

array and another master indicating

BUSYononeothersideofthearray.

This would inhibit the write operations from one port for part of a word and

inhibitthewriteoperationsfromtheotherportfortheotherpartoftheword.

The

BUSY arbitration, on a master, is based on the chip enable and

address signals only. It ignores whether an access is a read or write. In

a master/slave array, both address and chip enable must be valid long

enoughfora

BUSYflagtobeoutputfromthemasterbeforetheactualwrite

pulsecanbeinitiatedwitheithertheR/

Wsignalorthebyteenables.Failure

toobservethistimingcanresultinaglitchedinternalwriteinhibitsignaland

corrupted data in the slave.

Semaphores

The IDT70V35/34 (IDT70V25/24) is an extremely fast Dual-Port 8/

4K x 18 (8/4K x 16) CMOS Static RAM with an additional 8 address

locations dedicated to binary semaphore flags. These flags allow either

processorontheleftorrightsideoftheDual-PortSRAMtoclaimaprivilege

over the other processor for functions defined by the system designer’s

Functional Description

The IDT70V35/34 (IDT70V25/24) provides two ports with separate

control, address and I/O pins that permit independent access for reads or

writes to any location in memory. The IDT70V35/34 (IDT70V25/24) has

an automatic power down feature controlled by

CE. TheCEcontrolson-

chip power down circuitry that permits the respective port to go into a

standby mode when not selected (

CE HIGH). When a port is enabled,

access to the entire memory array is permitted.

Interrupts

Iftheuserchoosestheinterruptfunction,amemorylocation(mailbox

or message center) is assigned to each port. The left port interrupt flag

(

INTL) is asserted when the right port writes to memory location 1FFE

(HEX) (FFE for IDT70V34 and IDT70V24), where a write is defined as

the

CER=R/WR=VIL perTruthTableIII.Theleftportclearstheinterrupt

on the IDT70V35 and IDT70V25 by an address location 1FFE (FFE for

IDT70V34andIDT70V24)accesswhen

CEL=OEL=VIL,R/WLisa"don't

care". Likewise, the right port interrupt flag (

INTR)issetwhentheleftport

writestomemorylocation1FFFforIDT70V35andIDT70V25(HEX)(FFF

for IDT70V34 and IDT70V24) and to clear the interrupt flag (

INTR), the

right port must read the memory location 1FFF for IDT70V35 and

IDT70V25 (FFF for IDT70V34 and IDT70V24). The message (16 bits)

at 1FFE or 1FFF for IDT70V35 and IDT70V25 (FFE or FFF for

IDT70V34 and IDT70V24) is user-defined, since it is an addressable

SRAMlocation.Iftheinterruptfunctionisnotused,addresslocations1FFE

and 1FFF for IDT70V35 and IDT70V25 (FFE and FFF for IDT70V34 and

IDT70V24) are not used as mail boxes, but as part of the random access

memory. Refer to Truth Table III for the interrupt operation.

Busy Logic

BusyLogicprovidesahardwareindicationthatbothportsoftheSRAM

haveaccessedthesamelocationatthesametime.Italsoallowsoneofthe

twoaccessestoproceedandsignalstheothersidethattheSRAMis“busy”.

The

BUSYpincanthenbeusedtostalltheaccessuntiltheoperationon

the other side is completed. If a write operation has been attempted from

thesidethatreceivesa

BUSYindication,thewritesignalisgatedinternally

to prevent the write from proceeding.

The use of

BUSYlogicisnotrequiredordesirableforallapplications.

In some cases it may be useful to logically OR the

BUSYoutputstogether

and use any

BUSY indication as an interrupt source to flag the event of

an illegal or illogical operation. If the write inhibit function of

BUSYlogicis

5624 drw 19

MASTER

Dual Port

SRAM

BUSYL

BUSYR

CE

MASTER

Dual Port

SRAM

BUSYL

BUSYR

CE

SLAVE

Dual Port

SRAM

BUSYL

BUSYR

CE

SLAVE

Dual Port

SRAM

BUSYL

BUSYR

CE

BUSYL

BUSYR

D

E

C

O

D

E

R

,

相關PDF資料 |

PDF描述 |

|---|---|

| 710-405J12 | STEEL, CIRCULAR ADAPTER |

| 710-405J16 | STEEL, CIRCULAR ADAPTER |

| 710-405J24 | STEEL, CIRCULAR ADAPTER |

| 710-405J32 | STEEL, CIRCULAR ADAPTER |

| 710-405J40 | STEEL, CIRCULAR ADAPTER |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 70V34S25PF | 功能描述:靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 70V34S25PF8 | 功能描述:靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 70V3569S4BC | 功能描述:靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 70V3569S4BC8 | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Sync Dual 3.3V 576K-Bit 16K x 36 4.2ns 256-Pin CABGA T/R 制造商:Integrated Device Technology Inc 功能描述:SRAM SYNC DUAL 3.3V 576KBIT 16KX36 4.2NS 256BGA - Tape and Reel |

| 70V3569S4BF | 功能描述:靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。