- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄296205 > 70V05L35PF8 (INTEGRATED DEVICE TECHNOLOGY INC) 8K X 8 DUAL-PORT SRAM, 35 ns, PQFP64 PDF資料下載

參數(shù)資料

| 型號(hào): | 70V05L35PF8 |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | SRAM |

| 英文描述: | 8K X 8 DUAL-PORT SRAM, 35 ns, PQFP64 |

| 封裝: | 14 X 14 MM, 1.40 MM HEIGHT, TQFP-64 |

| 文件頁數(shù): | 14/22頁 |

| 文件大小: | 159K |

| 代理商: | 70V05L35PF8 |

6.42

IDT70V05S/L

High-Speed 3.3V 8K x 8 Dual-Port Static RAM

Industrial and Commercial Temperature Ranges

21

D0

2941 drw 19

D

Q

WRITE

D0

D

Q

WRITE

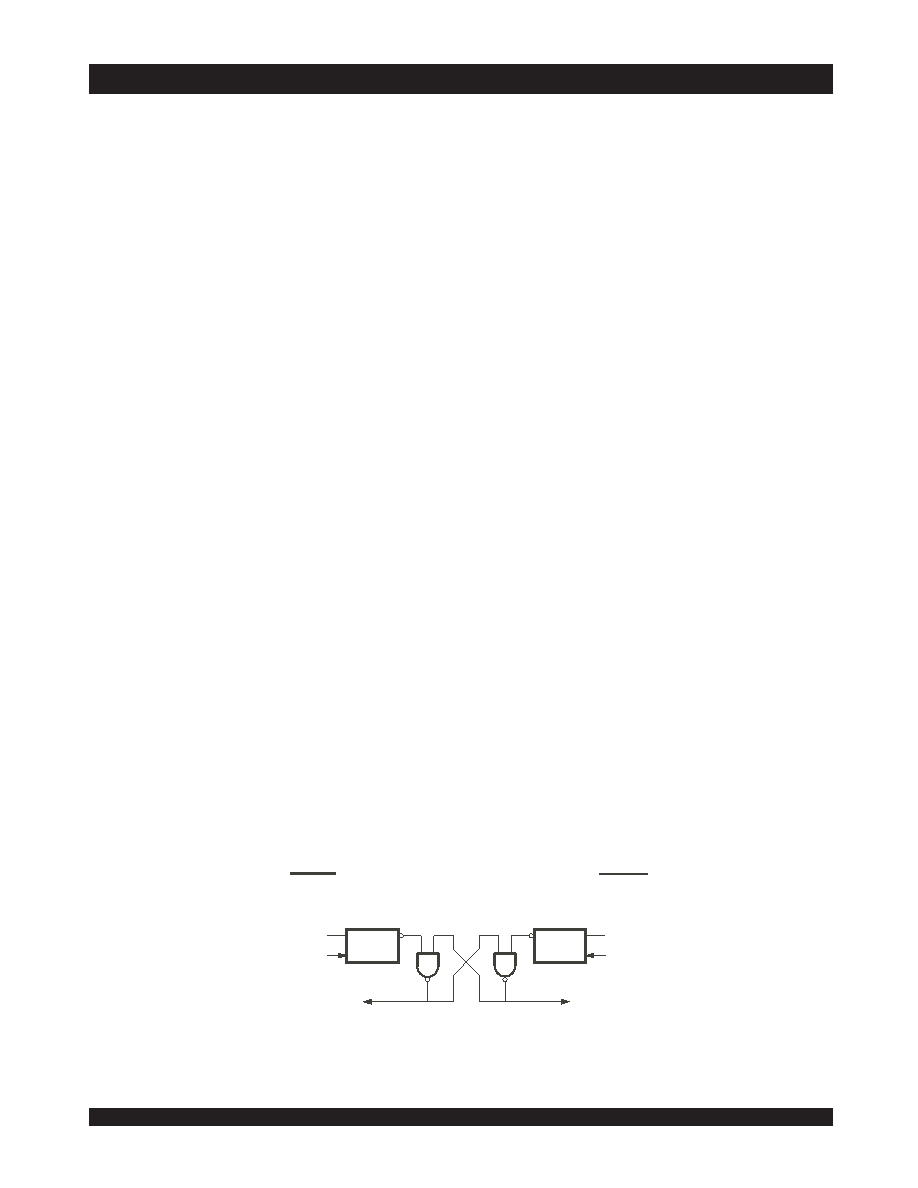

SEMAPHORE

REQUEST FLIP FLOP

SEMAPHORE

REQUEST FLIP FLOP

L PORT

R PORT

SEMAPHORE

READ

SEMAPHORE

READ

The critical case of semaphore timing is when both sides request a

single token by attempting to write a zero into it at the same time. The

semaphore logic is specially designed to resolve this problem. If

simultaneous requests are made, the logic guarantees that only one

side receives the token. If one side is earlier than the other in making

the request, the first side to make the request will receive the token. If

both requests arrive at the same time, the assignment will be arbitrarily

made to one port or the other.

One caution that should be noted when using semaphores is that

semaphores alone do not guarantee that access to a resource is

secure. As with any powerful programming technique, if semaphores

are misused or misinterpreted, a software error can easily happen.

Initialization of the semaphores is not automatic and must be

handled via the initialization program at power-up. Since any sema-

phore request flag which contains a zero must be reset to a one, all

semaphores on both sides should have a one written into them at

initialization from both sides to assure that they will be free when

needed.

UsingSemaphores—SomeExamples

Perhaps the simplest application of semaphores is their applica-

tion as resource markers for the IDT70V05’s Dual-Port SRAM. Say the

8K x 8 SRAM was to be divided into two 4K x 8 blocks which were to be

dedicated at any one time to servicing either the left or right port.

Semaphore 0 could be used to indicate the side which would control

the lower section of memory, and Semaphore 1 could be defined as the

indicator for the upper section of memory.

To take a resource, in this example the lower 4K of Dual-Port

SRAM, the processor on the left port could write and then read a

zero in to Semaphore 0. If this task were successfully completed

(a zero was read back rather than a one), the left processor would

assume control of the lower 4K. Meanwhile the right processor was

attempting to gain control of the resource after the left processor, it

would read back a one in response to the zero it had attempted to

write into Semaphore 0. At this point, the software could choose to try

andgaincontrolofthesecond4Ksectionbywriting,thenreadingazero

into Semaphore 1. If it succeeded in gaining control, it would lock out

theleftside.

Once the left side was finished with its task, it would write a one to

Semaphore 0 and may then try to gain access to Semaphore 1. If

Semaphore1wasstilloccupiedbytherightside,theleftsidecouldundo

itssemaphorerequestandperformothertasksuntilitwasabletowrite,then

readazerointoSemaphore1.Iftherightprocessorperformsasimilartask

withSemaphore0,thisprotocolwouldallowthetwoprocessorstoswap

4K blocks of Dual-Port SRAM with each other.

The blocks do not have to be any particular size and can even be

variable, depending upon the complexity of the software using the

semaphore flags. All eight semaphores could be used to divide the

Dual-PortSRAMorothersharedresourcesintoeightparts.Semaphores

can even be assigned different meanings on different sides rather than

being given a common meaning as was shown in the example above.

Semaphores are a useful form of arbitration in systems like disk

interfaces where the CPU must be locked out of a section of memory

during a transfer and the I/O device cannot tolerate any wait states.

With the use of semaphores, once the two devices has determined

which memory area was “off-limits” to the CPU, both the CPU and the

I/O devices could access their assigned portions of memory continu-

ously without any wait states.

Semaphores are also useful in applications where no memory

“WAIT” state is available on one or both sides. Once a semaphore

handshake has been performed, both processors can access their

assignedSRAMsegmentsatfullspeed.

Another application is in the area of complex data structures. In this

case, block arbitration is very important. For this application one

processor may be responsible for building and updating a data

structure. The other processor then reads and interprets that data

structure. If the interpreting processor reads an incomplete data

structure, a major error condition may exist. Therefore, some sort of

arbitration must be used between the two different processors. The

building processor arbitrates for the block, locks it and then is able to

go in and update the data structure. When the update is completed, the

data structure block is released. This allows the interpreting processor

to come back and read the complete data structure, thereby guaran-

teeing a consistent data structure.

Figure 4. IDT70V05 Semaphore Logic

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 70V05L20J | 8K X 8 DUAL-PORT SRAM, 20 ns, PQCC68 |

| 70V05L35PF | 8K X 8 DUAL-PORT SRAM, 35 ns, PQFP64 |

| 70V05S15J8 | 8K X 8 DUAL-PORT SRAM, 15 ns, PQCC68 |

| 70V05S55G | 8K X 8 DUAL-PORT SRAM, 55 ns, CPGA68 |

| 70V05S55J8 | 8K X 8 DUAL-PORT SRAM, 55 ns, PQCC68 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 70V05L35PFI | 制造商:Integrated Device Technology Inc 功能描述:SRAM ASYNC DUAL 3.3V 64KBIT 8KX8 35NS 64TQFP - Bulk |

| 70V05L35PFI8 | 功能描述:IC SRAM 64KBIT 64TQFP 制造商:idt, integrated device technology inc 系列:* 零件狀態(tài):最後搶購 標(biāo)準(zhǔn)包裝:750 |

| 70V05L55G | 制造商:Integrated Device Technology Inc 功能描述:SRAM ASYNC DUAL 3.3V 64KBIT 8KX8 55NS 68PIN PGA - Trays |

| 70V05L55J | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 8K x 8 3.3v Dual- Port Ram RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 70V05L55J8 | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 8K x 8 3.3v Dual- Port Ram RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。