- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371610 > 544M-01 Clock Divider PDF資料下載

參數(shù)資料

| 型號(hào): | 544M-01 |

| 英文描述: | Clock Divider |

| 中文描述: | 時(shí)鐘分頻器 |

| 文件頁(yè)數(shù): | 2/7頁(yè) |

| 文件大?。?/td> | 107K |

| 代理商: | 544M-01 |

Clock Divider

MDS 544M-01 A

2

Revision 041505

Integrated Circuit Systems, Inc.

●

525 Race Street, San Jose, CA 95126

●

tel (408) 297-1201

●

www.icst.com

ICS544-01

P R E L I M I N A R Y I N F O R M AT I O N

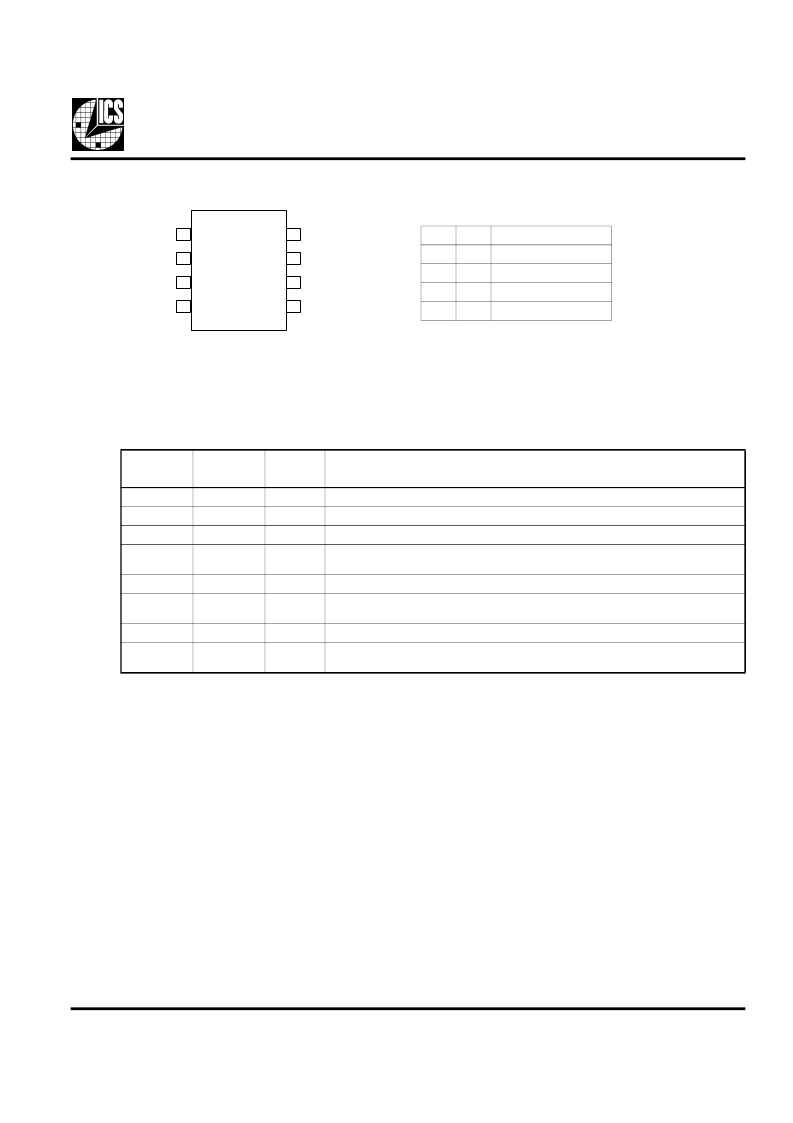

Pin Assignment

8-pin (150 mil) SOIC

Clock Divider Table

0 = connect directly to ground

1 = connect directly to VDD

Pin Descriptions

External Components

Series Termination Resistor

Clock output traces over one inch should use series

termination. To series terminate a 50

trace (a

commonly used trace impedance), place a 33

resistor

in series with the clock line, as close to the clock output

pin as possible. The nominal impedance of the clock

output is 20

.

On chip capacitors

- Crystal capacitors should be

connected from pins X1 to ground and X2 to ground to

optimize the initial accuracy. The value (in pf) of these

crystal caps equal (C

L

-12)*2 in this equation,

C

L

=crystal load capacitance in pf. For example, for a

crystal with a 16 pF load cap, each external crystal cap

would be 8 pF. [(16-12)x2]=8.

Decoupling Capacitor

As with any high-performance mixed-signal IC, the

ICS544-01 must be isolated from system power supply

noise to perform optimally.

A decoupling capacitor of 0.01μF must be connected

between VDD and the PCB ground plane.

PCB Layout Recommendations

For optimum device performance and lowest output

phase noise, the following guidelines should be

observed.

1) The 0.01μF decoupling capacitor should be mounted

on the component side of the board as close to the

X1/ICLK

X2

GND

VDD

S0

OE

CLK

S1

1

2

3

4

8

7

6

5

S1

0

0

1

1

S0

0

1

0

1

CLK

Input/32

Input/64

Input/256

Input/512

Pin

Number

1

2

3

Pin

Name

X1/ICLK

X2

GND

Pin

Type

XI

Xo

Power

Pin Description

Crystal or Clock input.

Connect to crystal for crystal input and leave open for clock input.

Connect to ground.

Select 0 for output clock. Connect to GND or VDD, per divider table above.

Internal pull-up resistor.

Clock output per table above.

Output Enable.Tri-states output clock when low. Also shuts down the oscillator

circuit. Internal pull-up resistor. OE=1 normal operation.

Connect to 2.25 V to 3.6 V.

Select 1 for output clock. Connect to GND or VDD, per divider table above.

Internal pull-up resistor.

4

S0

Input

5

CLK

Output

6

OE

Input

7

VDD

Power

8

S1

Input

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 544MI-01 | Clock Divider |

| 544MI01L | Clock Divider |

| 5451DM | Dual/Triple Ultra-Low-Voltage SOT23 µP Supervisory Circuits |

| 5451DMQB | Dual/Triple Ultra-Low-Voltage SOT23 µP Supervisory Circuits |

| 5451FMQB | Dual/Triple Ultra-Low-Voltage SOT23 µP Supervisory Circuits |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 544M01LF | 制造商:ICS 制造商全稱:ICS 功能描述:Clock Divider |

| 544M-01LF | 功能描述:時(shí)鐘驅(qū)動(dòng)器及分配 CLOCK DIVIDER RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| 544M-01LFT | 制造商:Integrated Device Technology Inc 功能描述:CLOCK DIVIDER 制造商:Integrated Device Technology Inc 功能描述:8 SOIC (GREEN) - Tape and Reel |

| 544M-01T | 制造商:Integrated Device Technology Inc 功能描述:CLOCK DIVIDER 8SOIC - Tape and Reel |

| 544MI-01 | 制造商:ICS 制造商全稱:ICS 功能描述:Clock Divider |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。