- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄115104 > 530HC340M000DG (SILICON LABORATORIES) CRYSTAL OSCILLATOR, CLOCK, 340 MHz, CMOS/TTL OUTPUT PDF資料下載

參數(shù)資料

| 型號(hào): | 530HC340M000DG |

| 廠商: | SILICON LABORATORIES |

| 元件分類: | XO, clock |

| 英文描述: | CRYSTAL OSCILLATOR, CLOCK, 340 MHz, CMOS/TTL OUTPUT |

| 封裝: | ROHS COMPLIANT, SMD, 6 PIN |

| 文件頁(yè)數(shù): | 7/12頁(yè) |

| 文件大?。?/td> | 215K |

| 代理商: | 530HC340M000DG |

Si530/531

4

Rev. 1.1

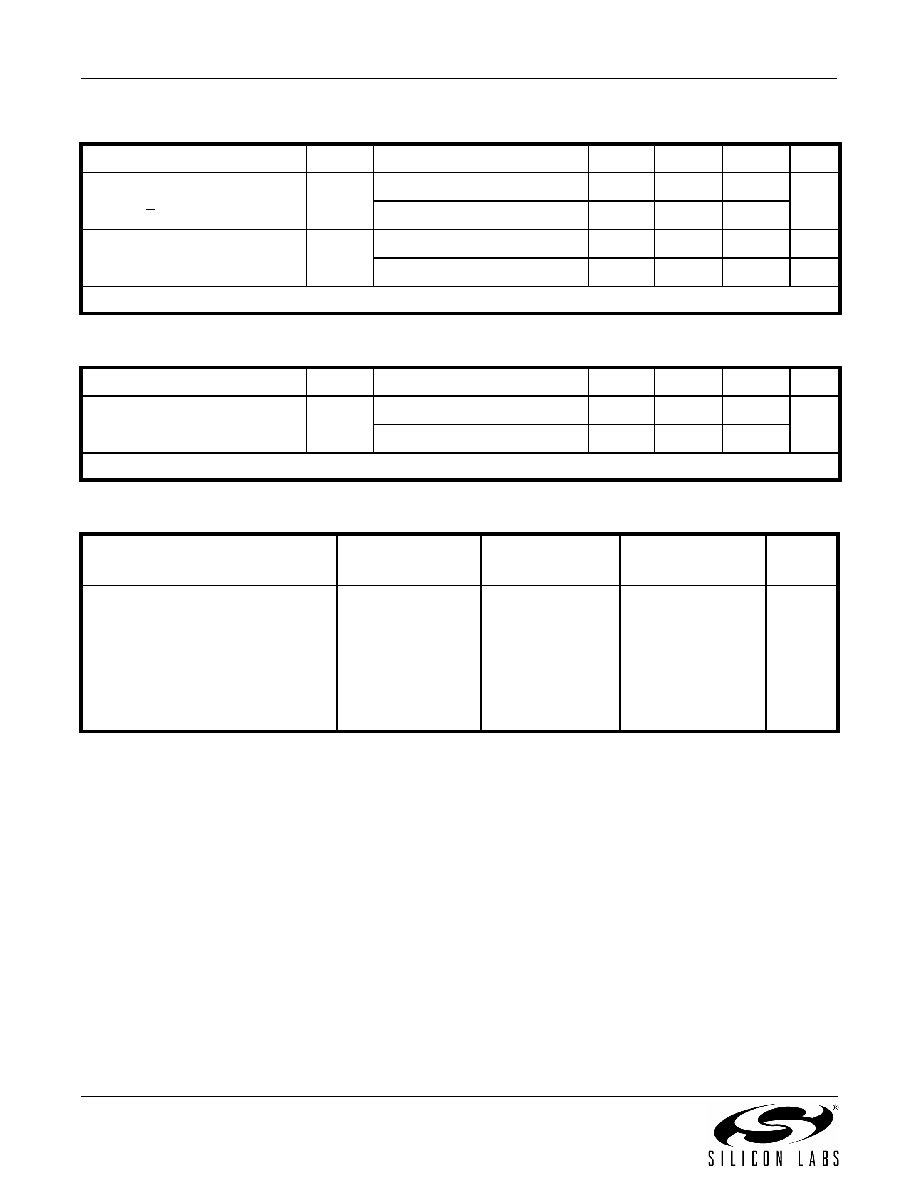

Table 4. CLK± Output Phase Jitter

Parameter

Symbol

Test Condition

Min

Typ

Max

Units

Phase Jitter (RMS)*

for FOUT > 500 MHz

φ

J

12 kHz to 20 MHz (OC-48)

—

0.25

0.40

ps

50 kHz to 80 MHz (OC-192)

—

0.26

0.37

Phase Jitter (RMS)*

for FOUT of 125 to 500 MHz

φ

J

12 kHz to 20 MHz (OC-48)

—

0.36

0.50

ps

50 kHz to 20 MHz (OC-192)

—

0.34

0.42

*Note: Differential Modes: LVPECL/LVDS/CML. Refer to AN256 for further information.

Table 5. CLK± Output Period Jitter

Parameter

Symbol

Test Condition

Min

Typ

Max

Units

Period Jitter*

JPER

RMS

—

2

—

ps

Peak-to-Peak

—

14

—

*Note: Any output mode, including CMOS, LVPECL, LVDS, CML. N = 1000 cycles. Refer to AN279 for further information.

Table 6. CLK± Output Phase Noise (Typical)

Offset Frequency (f)

120.00 MHz

LVDS

156.25 MHz

LVPECL

622.08 MHz

LVPECL

Units

100 Hz

1kHz

10 kHz

100 kHz

1MHz

10 MHz

100 MHz

–112

–122

–132

–137

–144

–150

n/a

–105

–122

–128

–135

–144

–147

n/a

–97

–107

–116

–121

–134

–146

–148

dBc/Hz

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 530HC438M000DGR | CRYSTAL OSCILLATOR, CLOCK, 438 MHz, CMOS/TTL OUTPUT |

| 530HC43M0000DGR | CRYSTAL OSCILLATOR, CLOCK, 43 MHz, CMOS/TTL OUTPUT |

| 530HC598M000DGR | CRYSTAL OSCILLATOR, CLOCK, 598 MHz, CMOS/TTL OUTPUT |

| 530HC631M000DGR | CRYSTAL OSCILLATOR, CLOCK, 631 MHz, CMOS/TTL OUTPUT |

| 531DA647M000DGR | CRYSTAL OSCILLATOR, CLOCK, 647 MHz, CMOS/TTL OUTPUT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 530HC500M000DG | 制造商:Silicon Laboratories Inc 功能描述:SMD CRYSTAL OSC 500MHZ 2.5V 6SMD - Trays |

| 530HC500M000DGR | 制造商:Silicon Laboratories Inc 功能描述:SMD CRYSTAL OSC 500MHZ 2.5V 6SMD - Tape and Reel |

| 530HC622M080DG | 功能描述:標(biāo)準(zhǔn)時(shí)鐘振蕩器 SINGLE XO 6 PIN 0.3PS RS JTR RoHS:否 制造商:AVX 產(chǎn)品:Standard Clock Oscillators 封裝 / 箱體:7 mm x 5 mm 頻率:75 MHz 頻率穩(wěn)定性:50 PPM 電源電壓:2.5 V 負(fù)載電容: 端接類型:SMD/SMT 最小工作溫度:0 C 最大工作溫度:+ 70 C 輸出格式:LVDS 尺寸: 封裝:Reel 系列: |

| 530HC622M080DGR | 制造商:Silicon Laboratories Inc 功能描述:OSCILLATOR - Tape and Reel |

| 530HC693M761DG | 制造商:Silicon Laboratories Inc 功能描述:OSCILLATOR - Trays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。