- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄371391 > 24AA128 (Microchip Technology Inc.) The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each PDF資料下載

參數(shù)資料

| 型號(hào): | 24AA128 |

| 廠商: | Microchip Technology Inc. |

| 元件分類: | EEPROM |

| 英文描述: | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| 中文描述: | 該CAT24FC02是一個(gè)2 KB的EEPROM的國(guó)內(nèi)256個(gè)8位每字舉辦的串行CMOS |

| 文件頁(yè)數(shù): | 7/12頁(yè) |

| 文件大小: | 185K |

| 代理商: | 24AA128 |

1998 Microchip Technology Inc.

DS21191B-page 7

24AA128/24LC128

6.0

WRITE OPERATIONS

6.1

Byte Write

Following the start condition from the master, the

control code (four bits), the chip select (three bits), and

the R/W bit (which is a logic low) are clocked onto the

bus by the master transmitter. This indicates to the

addressed slave receiver that the address high byte will

follow after it has generated an acknowledge bit during

the ninth clock cycle. Therefore, the next byte

transmitted by the master is the high-order byte of the

word address and will be written into the address

pointer of the 24xx128. The next byte is the least signif-

icant address byte. After receiving another acknowl-

edge signal from the 24xx128, the master device will

transmit the data word to be written into the addressed

memory location. The 24xx128 acknowledges again

and the master generates a stop condition. This ini-

tiates the internal write cycle, and, during this time, the

24xx128 will not generate acknowledge signals

(Figure 6-1). If an attempt is made to write to the array

with the WP pin held high, the device will acknowledge

the command but no write cycle will occur, no data will

be written, and the device will immediately accept a

new command. After a byte write command, the inter-

nal address counter will point to the address location

following the one that was just written.

6.2

Page Write

The write control byte, word address, and the first data

byte are transmitted to the 24xx128 in the same way as

in a byte write. But instead of generating a stop condi-

tion, the master transmits up to 63 additional bytes,

which are temporarily stored in the on-chip page buffer

and will be written into memory after the master has

transmitted a stop condition. After receipt of each word,

the six lower address pointer bits are internally

incremented by one. If the master should transmit more

than 64 bytes prior to generating the stop condition, the

address counter will roll over and the previously

received data will be overwritten. As with the byte write

operation, once the stop condition is received, an inter-

nal write cycle will begin (Figure 6-2). If an attempt is

made to write to the array with the WP pin held high, the

device will acknowledge the command but no write

cycle will occur, no data will be written, and the device

will immediately accept a new command.

6.3

Write Protection

The WP pin allows the user to write-protect the entire

array (0000-3FFF) when the pin is tied to V

CC

. If tied to

V

SS

or left floating, the write protection is disabled. The

WP pin is sampled at the STOP bit for every write

command (Figure 1-1) Toggling the WP pin after the

STOP bit will have no effect on the execution of the

write cycle.

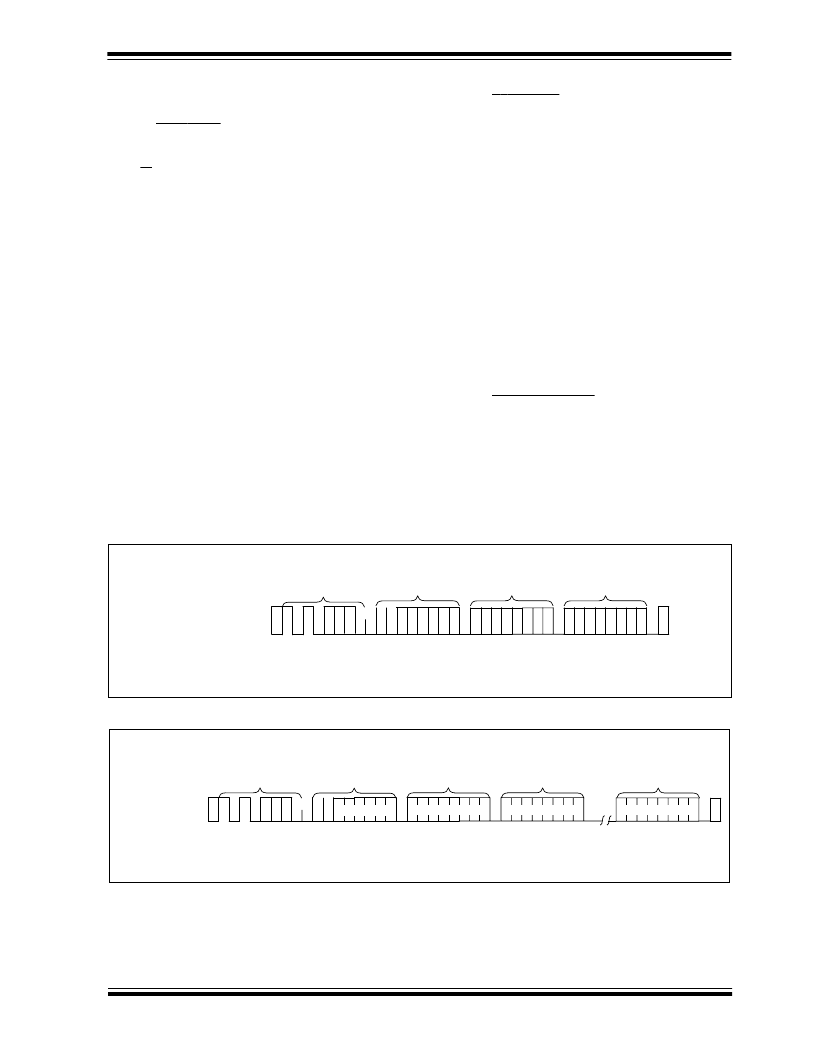

FIGURE 6-1:

BYTE WRITE

FIGURE 6-2:

PAGE WRITE

X X

BUS ACTIVITY

MASTER

SDA LINE

BUS ACTIVITY

S

T

A

R

T

CONTROL

BYTE

ADDRESS

HIGH BYTE

ADDRESS

LOW BYTE

DATA

S

T

O

P

A

C

K

A

C

K

A

C

K

A

C

K

X = don’t care bit

S 1 0 1 0

0

A

2

A

1

A

0

P

X X

BUS ACTIVITY

MASTER

SDA LINE

BUS ACTIVITY

S

T

A

R

T

CONTROL

BYTE

ADDRESS

HIGH BYTE

ADDRESS

LOW BYTE

DATA BYTE 0

S

T

O

P

A

C

K

A

C

K

A

C

K

A

C

K

DATA BYTE 63

A

C

K

X = don’t care bit

S 1 0 1 0

0

A

2

A

1

A

0

P

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 24AA128EP | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| 24AA128ESM | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| 24AA128ESN | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| 24AA128EST | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| 24AA128IP | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 24AA128/P | 功能描述:電可擦除可編程只讀存儲(chǔ)器 16kx8 - 1.8V RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| 24AA128/S15K | 制造商:Microchip Technology Inc 功能描述:128K, 16K X 8, 1.8V SER EE, DI - Gel-pak, waffle pack, wafer, diced wafer on film |

| 24AA128/SM | 功能描述:電可擦除可編程只讀存儲(chǔ)器 16kx8 - 1.8V RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| 24AA128/SN | 功能描述:電可擦除可編程只讀存儲(chǔ)器 16kx8 - 1.8V RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| 24AA128/W15K | 功能描述:電可擦除可編程只讀存儲(chǔ)器 128K, 16K X 8, 1.8V SER EE, WAFER RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。