- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄140371 > W7NCF02GH20IS5BG (MICROSEMI CORP-PMG MICROELECTRONICS) 128M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC PDF資料下載

參數(shù)資料

| 型號(hào): | W7NCF02GH20IS5BG |

| 廠商: | MICROSEMI CORP-PMG MICROELECTRONICS |

| 元件分類: | PROM |

| 英文描述: | 128M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

| 封裝: | CARD |

| 文件頁(yè)數(shù): | 11/13頁(yè) |

| 文件大小: | 172K |

| 代理商: | W7NCF02GH20IS5BG |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)

March 2007

Rev. 10

W7NCFxxx-H Series

7

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

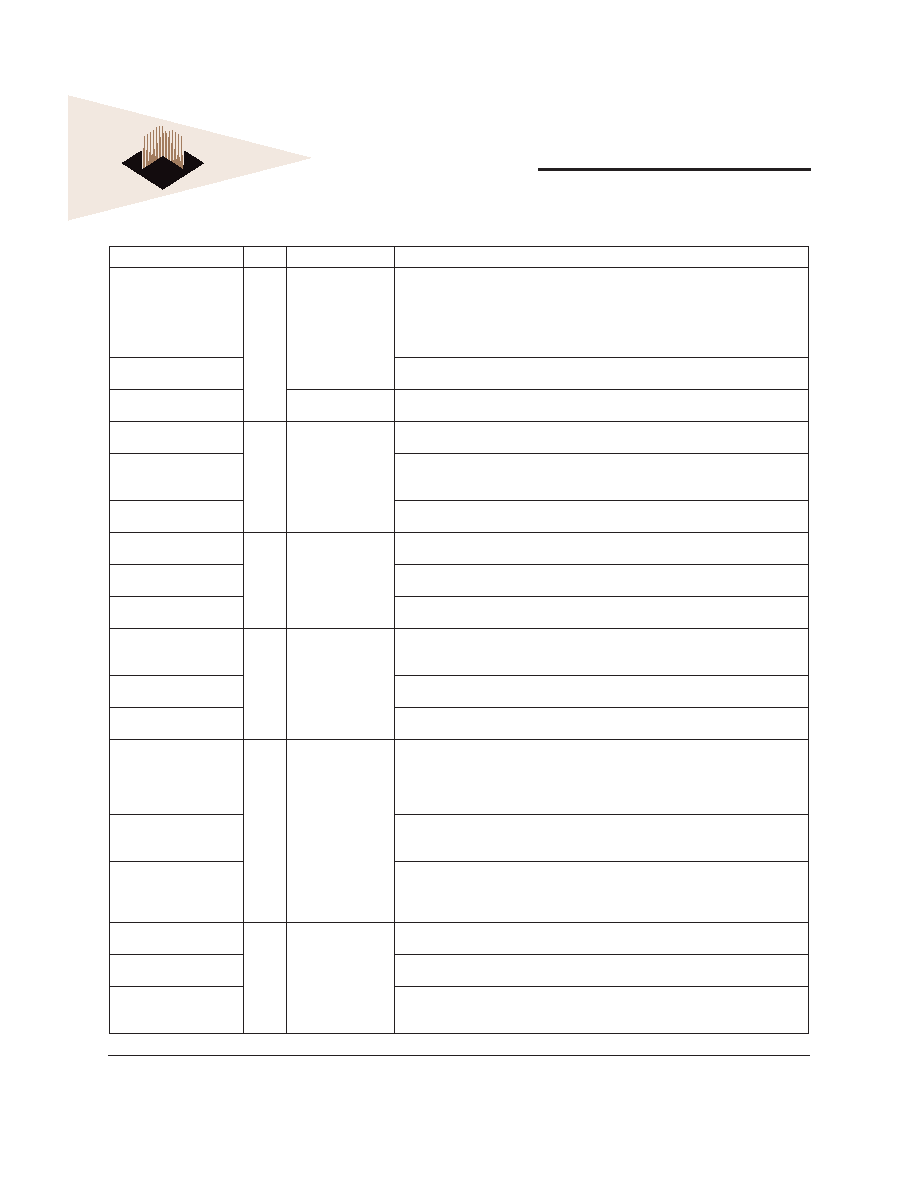

Signal Description

Signal Name

Dir.

Pin

Description

A10-A0

(PC Card Memory Mode)

I

8, 10, 11, 12, 14, 15,

16, 17, 18, 19, 20

These address lines along with the -REG signal are used to select the following: The I/O

port address registers within the CompactFlash Storage Card or CF+ Card, the memory

mapped port address registers within the CompactFlash Storage Card or CF+ Card, a byte

in the card's information structure and its conguration control and status registers.

A10-A0

(PC Card I/O Mode)

This signal is the same as the PC Card Memory Mode signal.

A2 - A0

(True IDE Mode)

18, 19, 20

In True IDE Mode, only A[2:0] are used to select the one of eight registers in the Task File,

the remaining address lines should be grounded by the host.

BVD1

(PC Card Memory Mode)

I/O

46

This signal is asserted high, as BVD1 is not supported.

-STSCHG

(PC Card I/O Mde)

Status Changed

This signal is asserted low to alert the host to changes in the READY and Write Protect

states , while the I/O interface is congured. Its use is controlled by the Card Cong and

Status Register.

-PDIAG

(True IDE Mode)

In the True IDE Mode, this input / output is the Pass Diagnostic signal in the Master / Slave

handshake protocol.

BVD2

(PC Card Memory Mode)

I/O

45

This signal is asserted high, as BVD2 is not supported.

-SPKR

(PC Card I/O Mode)

This line is the Binary Audio out put from the card. If the Card does not support the Binary

Audio function, this line should be held negated.

-DASP

(True IDE Mode)

In the True IDE Mode, this input/output is the Disk Active/Slave Present signal in the Master/

Slave handshake protocol.

-CD1, -CD2

(PC Card Memory Mode)

O

26, 25

These Card Detect pins are connected to ground on the CompactFlash Storage Card or

CF+ Card. They are used by the host to determine that the CompactFlash Storage Card or

CF+ Card is fully inserted into its socket.

-CD1, CD2

(PC Card I/O Mode)

This signal is the same for all modes.

-CD1, CD2

(True IDE Mode)

This signal is the same for all modes.

-CE1, -CE2

(PC Card Memory Mode)

Card Enable

I

7, 32

These input signals are used both to select the card and to indicate to the card whether

a byte or a word operation is being performed. -CE2 always accesses the odd byte of the

word. -CE1 accesses the even byte or the Odd byte of the word depending on A0 and -CE2.

A multiplexing scheme based on A0, -CE1, -CE2 allows 8 bit hosts to access all data on

D0-D7.

-CE1, -CE2

(PC Card I/O Mode)

Card Enable

This signal is the same as the PC Card Memory Mode signal.

-CS0, CS1

(True IDE Mode)

In the True IDE Mode, -CS0 is the chip select for the task le registers while -CS1 is used

to select the Alternate Status Register and the Device Control Register. While –DMACK is

asserted, -CS0 and –CS1 shall be held negated and the width of the transfers shall be 16

bits.

-CSEL

(PC Card Memory Mode)

I39

This signal is not used for this mode, but should be connected by the host to PC Card A25

or grounded by the host.

-CSEL

(PC Card I/O Mode)

This signal is not used for this mode, but should be connected by the host to PC Card A25

or grounded by the host.

-CSEL

(True IDE Mode)

This internally pulled up signal is used to congure this device as a Master or a Slave when

congured in the True IDE Mode. When this pin is grounded, this device is congured as a

Master. When the pin is open, this device is congured as a Slave.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W7NCF02GH20ISAJG | 128M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

| W7NCF08GH10CS8CG | 512M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

| W7NCF08GH10IS4DG | 512M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

| W7NCF08GH31IS4JG | 512M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

| W7NCF08GH31IS6EG | 512M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W7PCX-1 | 制造商:Magnecraft 功能描述:7PC Series Subminiature 2 A SPDT 5 VDC PCB Through Hole Switching Relay 制造商:Magnecraft 功能描述:Electromechanical Relay SPDT 2A 5VDC 75Ohm Through Hole |

| W7PCX-1/MMS105 | 制造商:Magnecraft 功能描述:Relay;E-Mech;Power;SPDT;Cur-Rtg 2A;Ctrl-V 5DC;Vol-Rtg 120/24AC/DC;PCB Mnt;5 Pin |

| W7PCX-3 | 制造商:Magnecraft 功能描述:Power Relay 制造商:Magnecraft 功能描述:Electromechanical Relay SPDT 2A 12VDC 440Ohm Through Hole |

| W7PCX-4 | 制造商:Magnecraft 功能描述:Electromechanical Relay SPDT 2A 24VDC 1.55KOhm Through Hole |

| W7PCX5 | 制造商:TE Magnecraft 功能描述:Relay 5 vdc DPDT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。