- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299790 > PSD402A2-C-15L (STMICROELECTRONICS) 32K X 16 UVPROM, 40 I/O, PIA-GENERAL PURPOSE, CQCC68 PDF資料下載

參數(shù)資料

| 型號(hào): | PSD402A2-C-15L |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32K X 16 UVPROM, 40 I/O, PIA-GENERAL PURPOSE, CQCC68 |

| 封裝: | WINDOWED, CERAMIC, LCC-68 |

| 文件頁(yè)數(shù): | 94/123頁(yè) |

| 文件大小: | 755K |

| 代理商: | PSD402A2-C-15L |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)當(dāng)前第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)

Obsolete

Product(s)

- Obsolete

Product(s)

PSD4XX Family

69

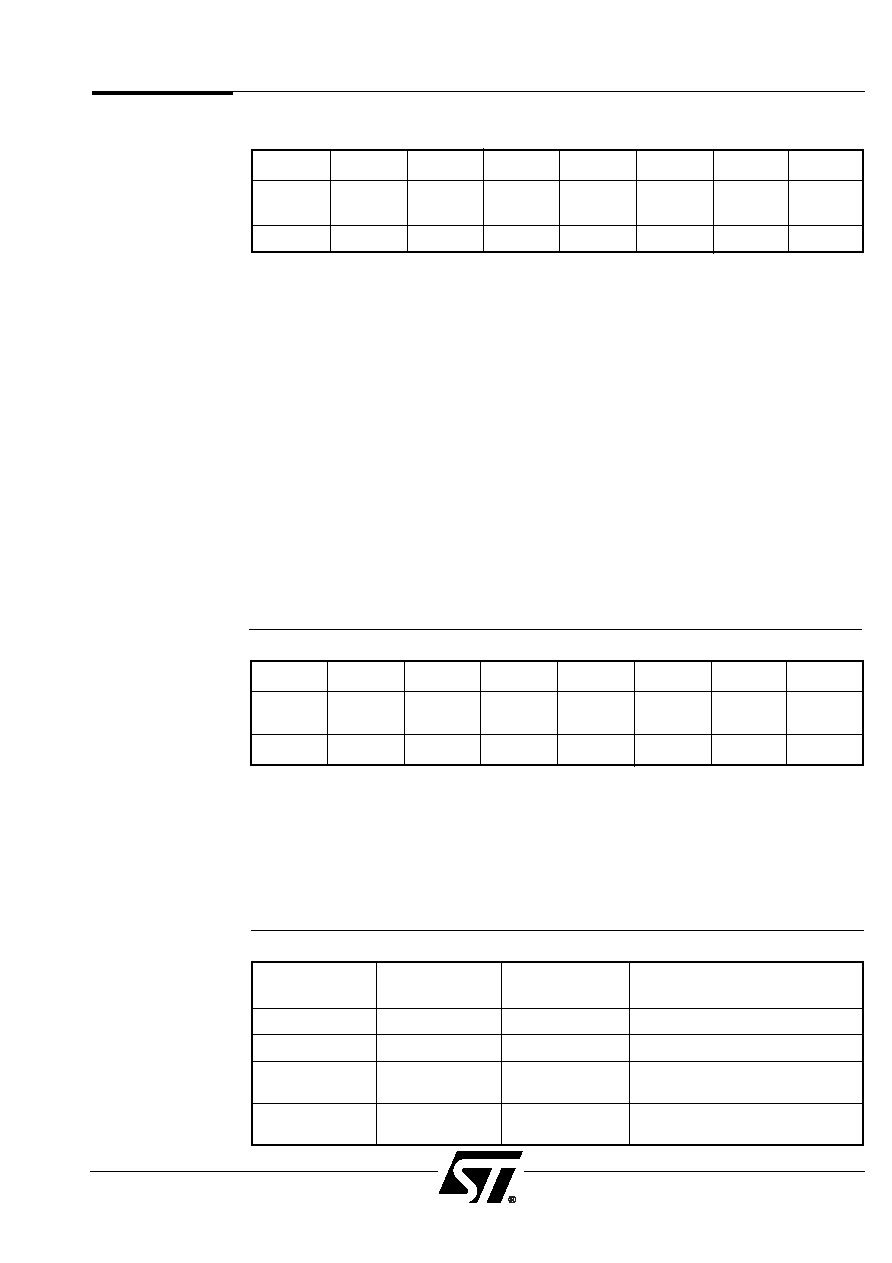

APD EN Bit

ALE Power

ALE Status

APD Counter

Down Polarity

0

X

Not Counting

1

X

Pulsing

Not Counting

11

1

Counting (Activates Standby

Mode After 15 Clocks)

10

0

Counting (Activates Standby

Mode After 15 Clocks)

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

TMR CLK

ZPLD

APD

ALE PD

*

RCLK

ACLK

TURBO

CMISER

ENABLE

Polarity

1 = OFF

1 = ON

1 = HIGH

PMMR0

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

*

***

**

Sleep

APD CLK

Mode

1 = ON

1 = CLKIN

PMMR1

Table 18. Power Management Mode Registers (PMMR0, PMMR1)

Table 19. APD Counter Operation

Bit 0 * = Should be set to High (1) to operate the APD.

Bit 1 0 = ALE Power Down (PD) Polarity Low.

1 = ALE Power Down (PD) Polarity High.

Bit 2 0 = Automatic Power Down (APD) Disable.

1 = Automatic Power Down (APD) Enable.

Bit 3 0 = EPROM/SRAM CMiser is OFF.

1 = EPROM/SRAM CMiser is ON.

Bit 4 0 = ZPLD Turbo is ON. ZPLD is always ON.

1 = ZPLD Turbo is OFF. ZPLD will Power Down when inputs are not changing.

Bit 5 0 = ZPLD Clock Input into the Array from the CLKIN pin input is connected.

Every Clock change will Power Up the ZPLD when Turbo bit is OFF.

1 = ZPLD Clock Input into the Array from the CLKIN pin input is disconnected.

Bit 6 0 = ZPLD Clock Input into the the MacroCell registers from the CLKIN pin input

is connected.

1 = ZPLD Clock Input into the the MacroCell registers from the CLKIN pin input

is disconnected.

Bit 7 * = In the PSD4XX should be set to High (1)

Bit 0

0 = Automatic Power Down Unit Clock is connected to Port E7 (PE7) alternate

function input.

1 = Automatic Power Down Unit Clock is connected to the PSD Clock

input (CLKIN).

Bit 1

0 = Sleep Mode Disabled.

1 = Sleep Mode Enabled.

Bit 2–7 0 = Reserved for future use, should be set to zero.

The PSD4XX

Architecture

(cont.)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PSD4235G2-A-15U | 4M X 1 FLASH, 52 I/O, PIA-GENERAL PURPOSE, PQFP80 |

| PSD4235G2-A-20UI | 4M X 1 FLASH, 52 I/O, PIA-GENERAL PURPOSE, PQFP80 |

| PSD813F2A-15JI | 128K X 8 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQCC52 |

| PSD834F2VA-15MI | 256K X 8 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQFP52 |

| PSD854F2A-90MT | 256K X 8 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQFP52 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PSD402A2-C-15U | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:Low Cost Field Programmable Microcontroller Peripherals |

| PSD402A2-C-70J | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:Low Cost Field Programmable Microcontroller Peripherals |

| PSD402A2-C-70L | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:Low Cost Field Programmable Microcontroller Peripherals |

| PSD402A2-C-70U | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:Low Cost Field Programmable Microcontroller Peripherals |

| PSD402A2-C-90JI | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:Low Cost Field Programmable Microcontroller Peripherals |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。