- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄65818 > MSP50C605PJM (TEXAS INSTRUMENTS INC) 0-BIT, 12.32 MHz, MIXED DSP, PQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | MSP50C605PJM |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 數(shù)字信號(hào)處理 |

| 英文描述: | 0-BIT, 12.32 MHz, MIXED DSP, PQFP100 |

| 封裝: | PLASTIC, QFP-100 |

| 文件頁數(shù): | 2/9頁 |

| 文件大?。?/td> | 121K |

| 代理商: | MSP50C605PJM |

MSP50C605

MIXED-SIGNAL PROCESSOR

SPSS025B– FEBRUARY 2000 – REVISED FEBRUARY 2001

2

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

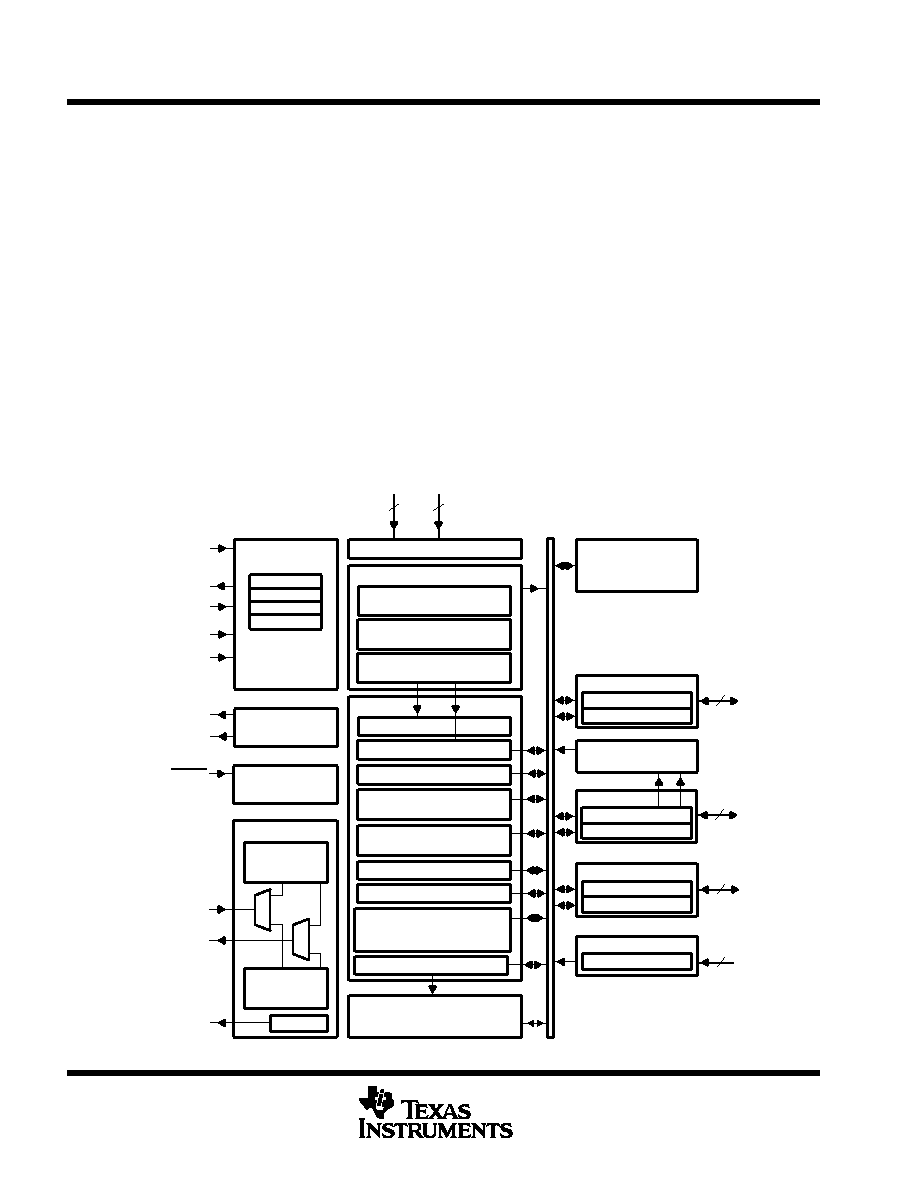

description (continued)

A flexible clock generation system enables the software to control the clock over a wide frequency range. The

implementation uses a phase-locked loop (PLL) circuit that drives the processor clock at a selectable frequency

between the minimum and maximum achievable. Selectable frequencies for the processor clock are spaced

apart in 65.536 kHz steps. The PLL clock-reference is also selectable; either a resistor-trimmed oscillator or a

crystal-referenced oscillator may be used. Internal and external clock sources are controlled separately to

provide different levels of power management.

The periphery consists of three 8-bit wide general-purpose I/O ports and one 8-bit wide dedicated input port.

The bidirectional I/O can be configured under software control as either high-impedance inputs or as totem-pole

outputs. They are controlled via addressable I/O registers. The input-only port has a programmable pullup

option (70-k

minimum resistance) and a dedicated service interrupt. These features make the input port

especially useful as a key-scan interface.

A simple one-bit comparator is also included in the periphery. The comparator is enabled by a control register,

and its pin access is shared with two pins in one of the general-purpose I/O ports. Rounding out the MSP50C605

periphery is a built-in pulse-density-modulated DAC (digital-to-analog converter) with direct speaker-drive

capability. The functional block diagram gives an overview of the MSP50C605 functionality.

functional block diagram

SCANIN

SYNC

PLL

OSCOUT

OSCIN

RESET

DACM

DACP

TEST

SCANCLK

SCANOUT

Serial Comm.

OTP Program

Emulation

Break Point

DAC

0x30

32

PDM

Initialization

Logic

OSC Reference

Resistor

Trimmed

32 kHz nominal

Crystal

Referenced

32.768 kHz

PLL Filter

or

Scan Interface

Power

VDD

VSS

45

(EP)ROM

32k x (16 + 1) bit

Test-Area

(reserved)

0x0000 to

0x07FF

User ROM

0x0800 to

0x7FEF

INT vectors

0x7FF0 to

0x7FFF

Core

Instr. Decoder

PCU

Prog. Counter Unit

CU

Computational Unit

TIMER1

PRD1

0x3A

TIM1

0x3B

TIMER2

PRD2

0x3E

TIM2

0x3F

Clock Control

0x3D

Gen. Control

0x38

Interrupt Processor

FLAG

0x39

MASK

0x38

DMAU

Data Mem. Addr.

RAM 640 x 17 bit

(data)

0x000 to

0x027F

224K bytes

Data ROM

C port I/O

Data

0x10

Control

0x14

Comparator

1 bit: PD5 vs PD4

D port I/O

Data

0x18

Control

0x1C

E port I/O

Data

0x20

Control

0x24

F port INPUT

Data

0x28

8

PC0–7

8

PD0–7

8

PE0–7

8

PF0–7

+

–

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSP50C614PJM | 0-BIT, 12.32 MHz, MIXED DSP, PQFP100 |

| MSS-40,346-B21 | SILICON, MIXER DIODE |

| MSS1P2U-M3/89A | 1 A, 20 V, SILICON, SIGNAL DIODE |

| MSS1P6HM3/89A | 1 A, 60 V, SILICON, SIGNAL DIODE |

| MTD-0818-M33-1 | SILICON, C-KU BAND, MIXER DIODE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSP50C614 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:MIXED-SIGNAL PROCESSOR |

| MSP50P34 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Mixed-Signal Processors |

| MSP50P34DWE1A | 制造商:Texas Instruments 功能描述: |

| MSP50P34DWI2D | 制造商:Texas Instruments 功能描述: |

| MSP50P34N | 制造商:Texas Instruments 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。