- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄366330 > ACM1602T (AZ Displays, Inc.) JT 24C 12#16 12#12 SKT WALL RE PDF資料下載

參數(shù)資料

| 型號(hào): | ACM1602T |

| 廠商: | AZ Displays, Inc. |

| 英文描述: | JT 24C 12#16 12#12 SKT WALL RE |

| 中文描述: | 規(guī)格液晶顯示器 |

| 文件頁(yè)數(shù): | 7/10頁(yè) |

| 文件大小: | 283K |

| 代理商: | ACM1602T |

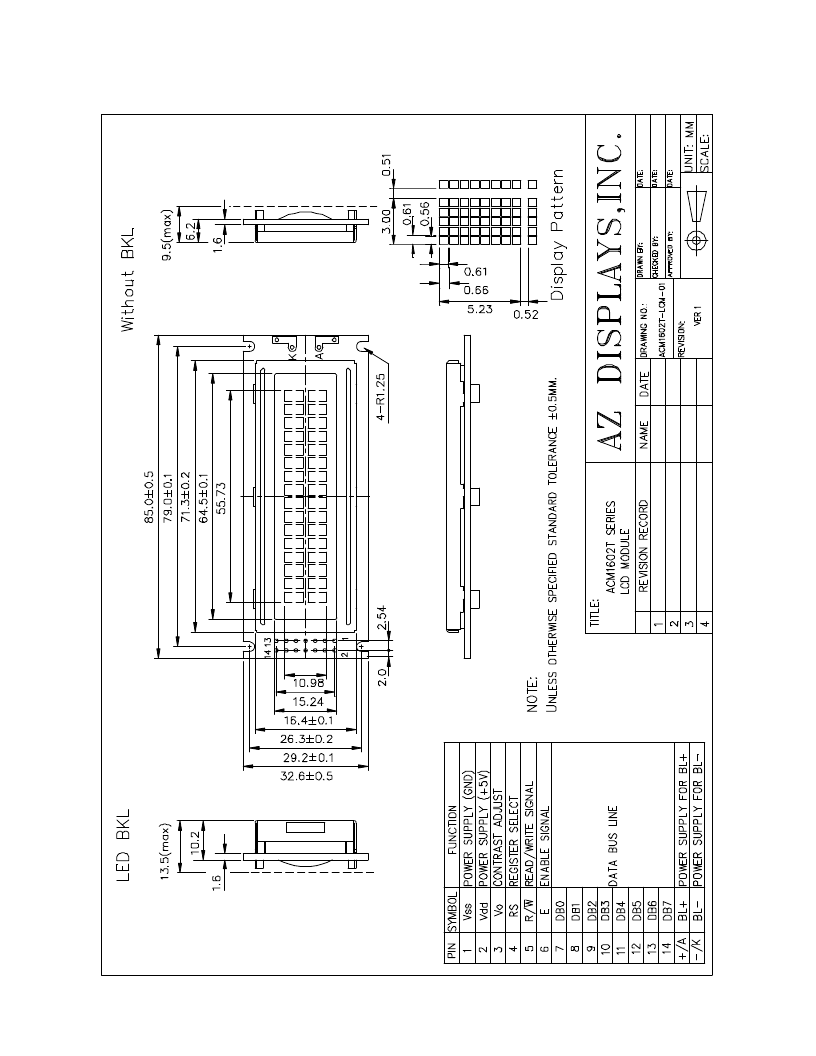

ACM1602T SERIES LCD MODULE

AZ DISPLAYS, INC.

09/17/99

6

9.0 MECHANICAL DIAGRAM

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ACM1602U | SPECIFICATIONS FOR LIQUID CRYSTAL DISPLAY |

| ACM1602V | Circular Connector; MIL SPEC:MIL-DTL-38999 Series II; Body Material:Metal; Series:JT; No. of Contacts:100; Connector Shell Size:24; Connecting Termination:Crimp; Circular Shell Style:Straight Plug; Body Style:Straight RoHS Compliant: No |

| ACM1602W | ACM1602W SERIES LCD MODULE |

| ACM1602Y | ECONOLINE: RB & RA - Dual Output from a Single Input Rail- Power Sharing on Output- Industry Standard Pinout- 1kVDC & 2kVDC Isolation- Custom Solutions Available- UL94V-0 Package Material- Efficiency to 85% |

| ACM1602Z | SPECIFICATIONS FOR LIQUID CRYSTAL DISPLAY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ACM1602U | 制造商:AZDISPLAYS 制造商全稱(chēng):AZ Displays 功能描述:SPECIFICATIONS FOR LIQUID CRYSTAL DISPLAY |

| ACM1602U-RN-GBH | 制造商:AZDISPLAYS 制造商全稱(chēng):AZ Displays 功能描述:STANDARD CHIP-ON-GLASS DISPLAYS |

| ACM1602V | 制造商:AZDISPLAYS 制造商全稱(chēng):AZ Displays 功能描述:ACM1602V SERIES LCD MODULE |

| ACM1602W | 制造商:AZDISPLAYS 制造商全稱(chēng):AZ Displays 功能描述:ACM1602W SERIES LCD MODULE |

| ACM1602Y | 制造商:AZDISPLAYS 制造商全稱(chēng):AZ Displays 功能描述:SPECIFICATIONS FOR LIQUID CRYSTAL DISPLAY |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。