- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄374361 > KM718V949 (SAMSUNG SEMICONDUCTOR CO. LTD.) 512Kx18-Bit No Turnaround SRAM(512Kx18位數(shù)據(jù)流無(wú)返回靜態(tài) RAM) PDF資料下載

參數(shù)資料

| 型號(hào): | KM718V949 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 512Kx18-Bit No Turnaround SRAM(512Kx18位數(shù)據(jù)流無(wú)返回靜態(tài) RAM) |

| 中文描述: | 512Kx18位無(wú)轉(zhuǎn)機(jī)的SRAM(512Kx18位數(shù)據(jù)流無(wú)返回靜態(tài)內(nèi)存) |

| 文件頁(yè)數(shù): | 2/17頁(yè) |

| 文件大小: | 276K |

| 代理商: | KM718V949 |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)

PRELIMINARY

KM736V849

KM718V949

256Kx36 & 512Kx18 Pipelined N

t

RAM

TM

- 2 -

Rev 0.1

Aug. 1998

256Kx36 & 512Kx18-Bit N

t

RAM

TM

The KM736V849 and KM718V949 are 9,437,184 bits Synchro-

nous Static SRAMs.

The N

t

RAM

TM

, or No Turnaround Random Access Memory uti-

lizes all the bandwidth in any combination of operating cycles.

Address, data inputs, and all control signals except output

enable and linear burst order are synchronized to input clock.

Burst order control must be tied "High or Low".

Asynchronous inputs include the sleep mode enable(ZZ).

Output Enable controls the outputs at any given time.

Write cycles are internally self-timed and initiated by the rising

edge of the clock input. This feature eliminates complex off-chip

write pulse generation

and provides increased timing flexibility for incomming signals.

For read cycles, pipelined SRAM output data is temporarily

stored by an edge trigered output register and then released to

the output bufferes at the next rising edge of clock.

The KM736V849 and KM718V949 are implemented with SAM-

SUNG

′

s high performance CMOS technology and is available

in 100pin TQFP packages. Multiple power and ground pins

minimize ground bounce.

GENERAL DESCRIPTION

FEATURES

3.3V+0.165V/-0.165V Power Supply.

I/O Supply Voltage 3.3V+0.165V/-0.165V for 3.3V I/O

or 2.5V+0.4V/-0.125V for 2.5V I/O.

Byte Writable Function.

Enable clock and suspend operation.

Single READ/WRITE control pin.

Self-Timed Write Cycle.

Three Chip Enable for simple depth expansion with no data

contention

Α

interleaved burst or a linear burst mode.

Asynchronous output enable control.

Power Down mode.

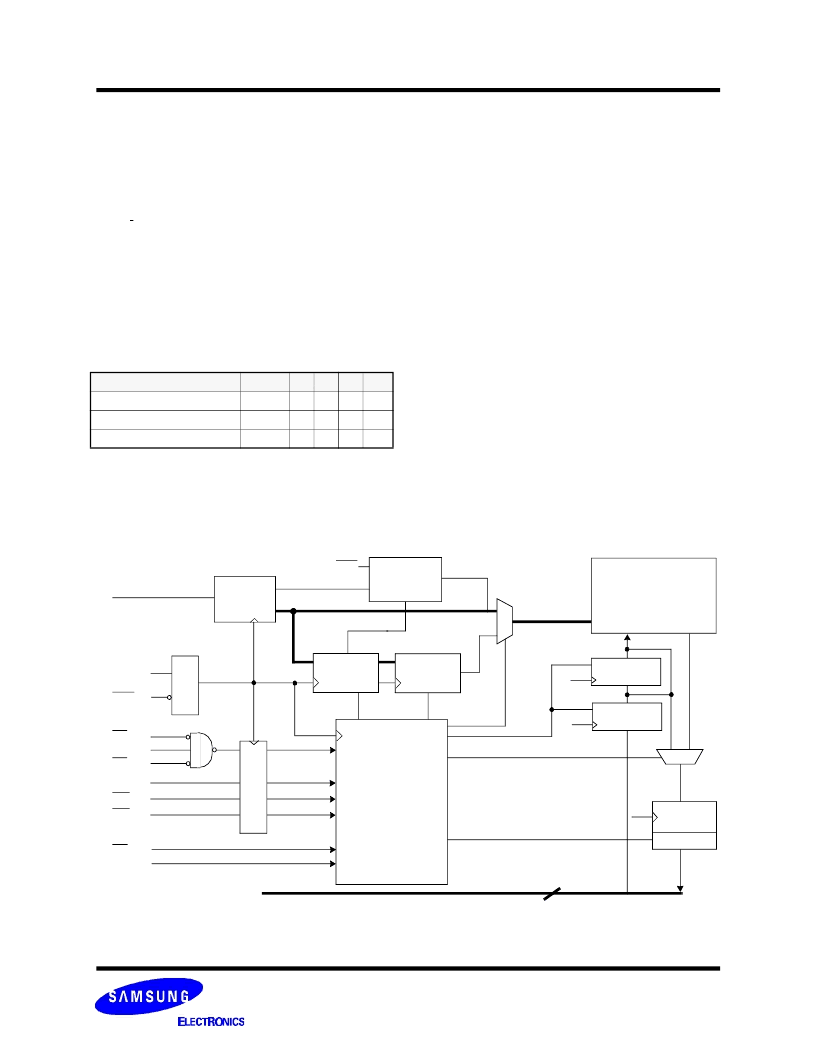

LOGIC BLOCK DIAGRAM

FAST ACCESS TIMES

Parameter

Symbol

-67 -75 -10 Unit

Cycle Time

t

CYC

6.7

7.5

10

ns

Clock Access Time

t

CD

3.8

4.0

5.0

ns

Output Enable Access Time

t

OE

3.8

4.0

5.0

ns

WE

BW

(x=a,b,c,d or a,b)

CLK

CKE

CS

1

CS

2

CS

2

ADV

OE

ZZ

DQa

~ DQd

or

DQa

0

~ DQb

8

DQPa ~ DQPd

ADDRESS

REGISTER

ADDRESS

REGISTER

C

L

A

′

0

~A

′

1

36 or 18

OUTPUT

REGISTER

BUFFER

DATA-IN

REGISTER

DATA-IN

REGISTER

K

K

K

BURST

ADDRESS

COUNTER

WRITE

ADDRESS

REGISTER

WRITE

CONTROL

LOGIC

C

R

K

A [0:17]or

A [0:18]

LBO

A

0

~A

1

A

2

~A

17

or

A

2

~A

18

256Kx36/512Kx18

MEMORY

ARRAY

N

t

RAM

TM

and No Turnaround RAM are trademarks of Samsung Electronics Co.,Ltd.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KM718V990 | 512Kx18 Synchronous SRAM(512Kx18位同步靜態(tài) RAM) |

| KM732V589L | 32Kx32 Synchronous SRAM |

| KM732V595A | 32Kx32 Synchronous SRAM |

| KM732V595L | 32Kx32 Synchronous SRAM |

| KM732V596A | 32Kx32 Synchronous SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KM718V987 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Kx36 & 512Kx18 Synchronous SRAM |

| KM7-19-20PN | 制造商:Amphenol Corporation 功能描述:KM AUSTRALIAN PRODUCT - Bulk |

| KM7-19-20PN-MK2 | 制造商:Amphenol Corporation 功能描述:KM AUSTRALIAN PRODUCT - Bulk |

| KM7-19-20SN | 制造商:Amphenol Corporation 功能描述:KM AUSTRALIAN PRODUCT - Bulk |

| KM7-19-20SN-MK2 | 制造商:Amphenol Corporation 功能描述:KM AUSTRALIAN PRODUCT - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。