- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374275 > K4J52324QC (SAMSUNG SEMICONDUCTOR CO. LTD.) 512Mbit GDDR3 SDRAM PDF資料下載

參數(shù)資料

| 型號: | K4J52324QC |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 512Mbit GDDR3 SDRAM |

| 中文描述: | 512MB的GDDR3 SDRAM的 |

| 文件頁數(shù): | 29/57頁 |

| 文件大小: | 1246K |

| 代理商: | K4J52324QC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁

- 29 -

Rev 1.0 (Mar 2005)

512M GDDR3 SDRAM

K4J52324QC-B

READs

READ bursts are initiated with a READ command, as below figure. The start-

ing column and bank addresses are provided with the READ command and

auto precharge is either enabled or disabled for that burst access. If auto pre-

charge is enabled, the row being accessed is prechrged at the completion of

the burst after t

RAS(min)

has been met. For the generic READ commands used

in the following illustrations, auto precharge is disabled.

During READ bursts, the valid data-out element from the starting column

address will be available following the CAS Latency after the READ com-

mand. Each subsequent data-out element will be valid nominally at the next

positive or negative strobe edge. READ burst figure shows general timing for

2 of the possible CAS latency settings. The GDDR3(x32) drives the output

data edge aligned to the crossing of CK and /CK and to RDQS. The initial

HIGH transitioning LOW of RDQS is known as the read preamble ; the half

cycle coincident with the last data-out element is known as the read postam-

ble.

Upon completion of a burst, assuming no other commands have been initi-

ated, the DQs will go High-Z. A detailed explanation of t

DQSQ

(valid data-out

skew), t

DV

(data-out window hold), the valid data window are depicted in Data

Output Timing (1) figure. A detailed explanation of t

AC

(DQS and DQ transition

skew to CK) is shown in Data Output Timing (2) figure.

Data from any READ burst may be concatenated with data from a subse-

quent READ command. A continuous flow of data can be maintained. The

first data element from the new burst follows the last element of a completed

burst. The new READ command should be issued x cycles after the first

READ command, where x equals the number of data element nibbles (nibbles

are required by the 4

n

-prefetch architecture) depending on the burst length.

This is shown in consecutive READ bursts figure. Nonconsecutive read data

is shown for illustration in nonconsecutive READ bursts figure. Full-speed

random read accesses within a page (or pages) can be performed as shown

in Random READ accesses figure. Data from a READ burst cannot be termi-

nated or truncated.

During READ commands the GDDR3 Dram disables its data terminators.

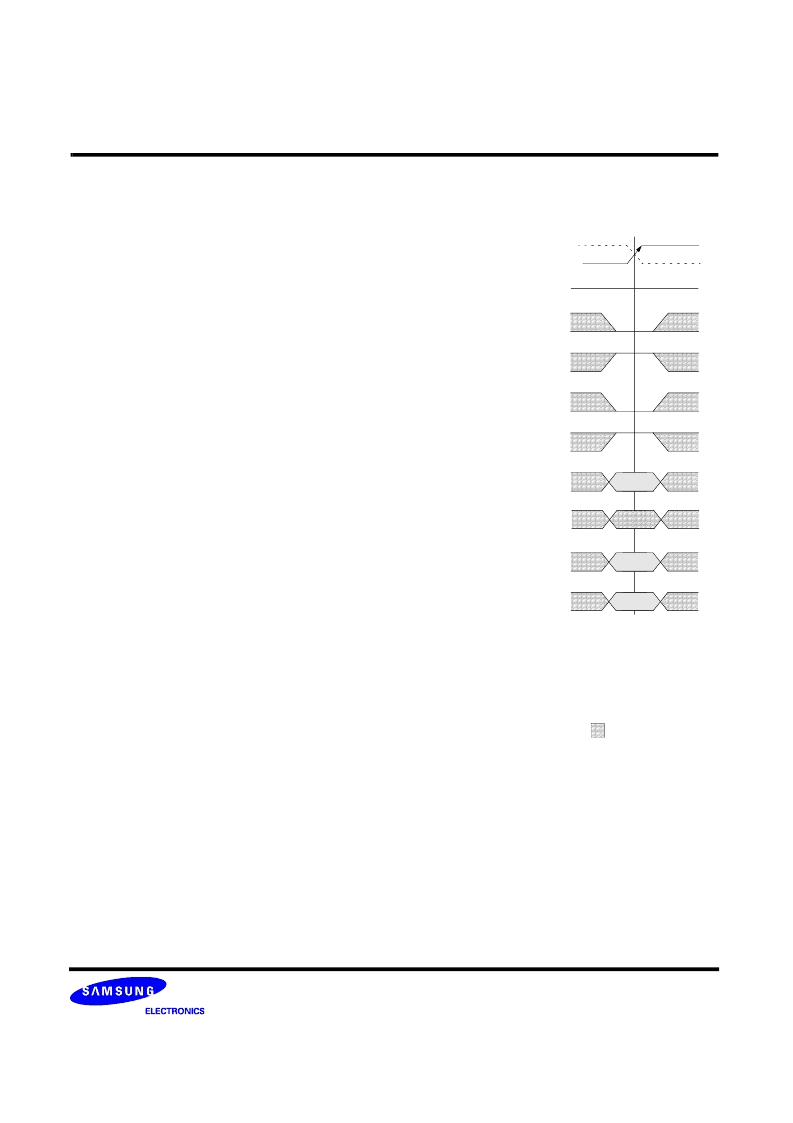

/CK

CK

CA

EN AP

DIS AP

BA

/CS

/RAS

/CAS

/WE

A0-A7, A9

A10, A11

A8

BA0,1,2

CA = Column Address

BA = Bank Address

EN AP = Enable Auto Precharge

DIS AP = Disable Auto Precharge

CKE

HIGH

DON’T CARE

READ Command

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K4J52324QC-BC14 | 512Mbit GDDR3 SDRAM |

| K4J52324QC-BC16 | 512Mbit GDDR3 SDRAM |

| K4J52324QC-BC20 | 512Mbit GDDR3 SDRAM |

| K4J52324QC-BJ12 | 512Mbit GDDR3 SDRAM |

| K4J52324QC-BJ14 | 512Mbit GDDR3 SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K4J52324QC-AC20000 | 制造商:Samsung Semiconductor 功能描述:GDDR3 SDRAM X32 BOC - Trays |

| K4J52324QC-BC14 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Mbit GDDR3 SDRAM |

| K4J52324QC-BC14000 | 制造商:Samsung Semiconductor 功能描述:GDDR3 SDRAM X32 BOC LEAD PART 10W - Trays |

| K4J52324QC-BC16 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Mbit GDDR3 SDRAM |

| K4J52324QC-BC20 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Mbit GDDR3 SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。