- 32 -

REV. 1.0 November. 2. 2000

128Mb DDR SDRAM

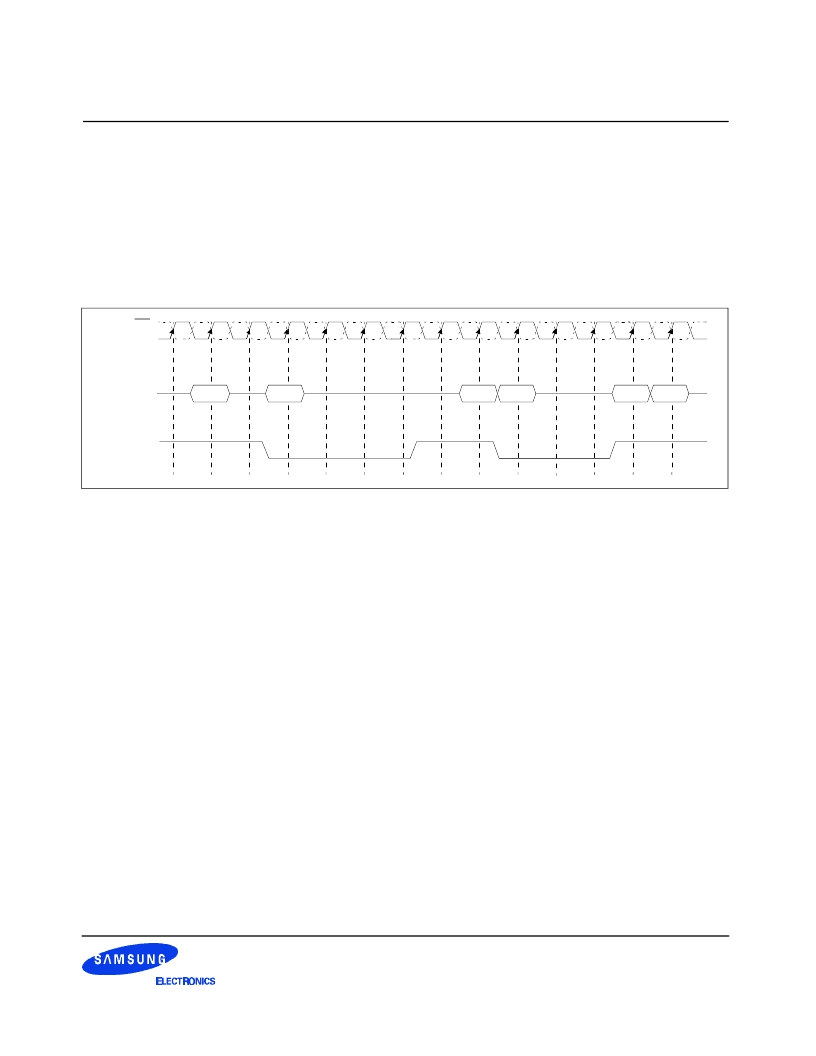

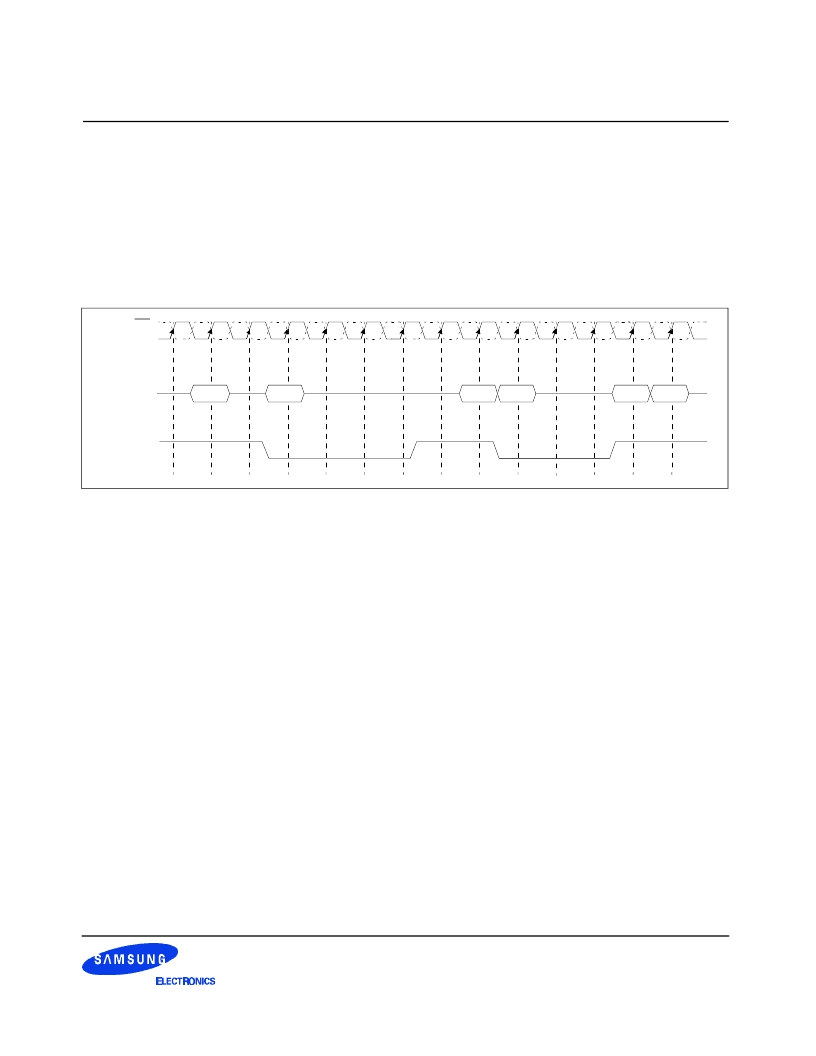

3.3.14 Power down

CKE

Precharge

Active

Active

power

down

Exit

Read

Active

power

down

Entry

power

down

Entry

Precharge

Command

~

~

~

~

~

~

CK

CK

The power down mode is entered when CKE is low and exited when CKE is high. Once the power down

mode is initiated, all of the receiver circuits except clock, CKE and DLL circuit tree are gated off to reduce

power consumption. All banks should be in idle state prior to entering the precharge power down mode and

CKE should be set high at least 1tck+tIS prior to row active command . During power down mode, refresh

operations cannot be performed, therefore the device cannot be remained in power down mode longer than

the refresh period(Data retension time) of the device.

Figure 23. Power down entry and exit timing