- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374254 > K4B1G1646C-ZCF7 (SAMSUNG SEMICONDUCTOR CO. LTD.) 1Gb C-die DDR3 SDRAM Specification PDF資料下載

參數(shù)資料

| 型號: | K4B1G1646C-ZCF7 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 1Gb C-die DDR3 SDRAM Specification |

| 中文描述: | 1Gb的?芯片的DDR3 SDRAM規(guī)范 |

| 文件頁數(shù): | 19/63頁 |

| 文件大小: | 1255K |

| 代理商: | K4B1G1646C-ZCF7 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁

Page 19 of 63

Rev. 1.0 June 2007

1Gb DDR3 SDRAM

K4B1G04(08/16)46C

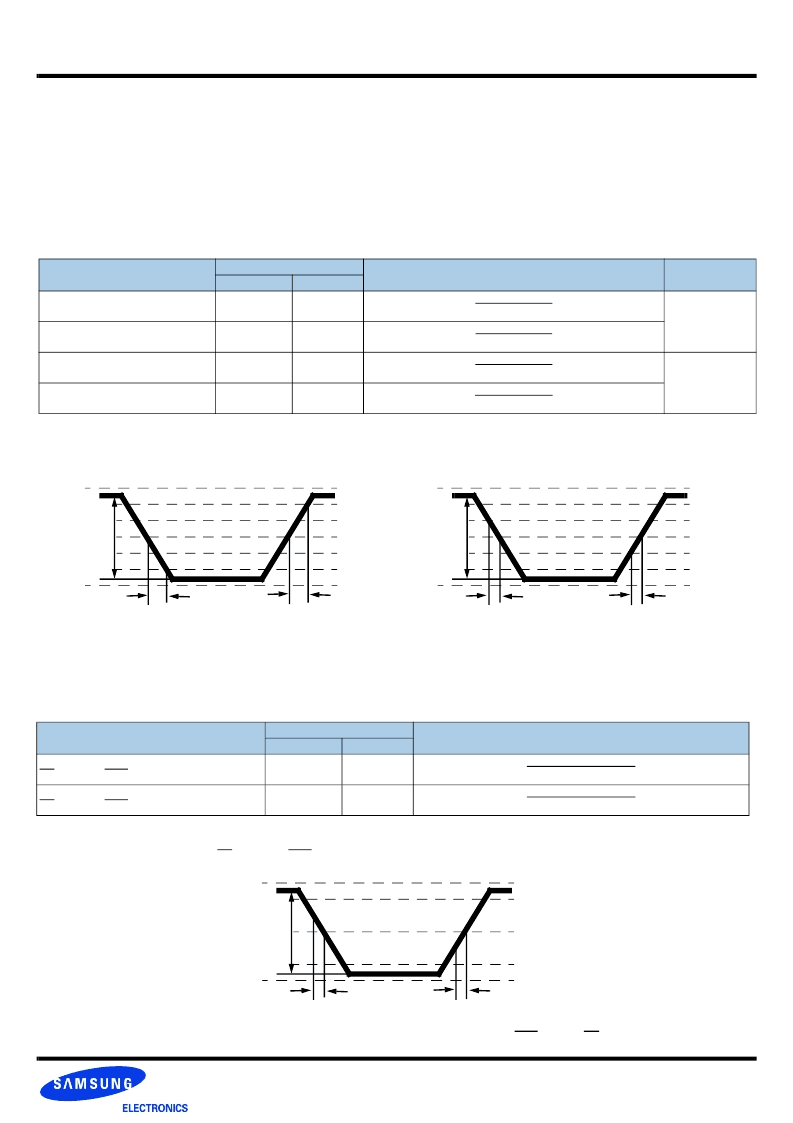

8.5.1 Input Slew Rate for Input Setup Time (tIS) and Data Setup Time (tDS)

Setup (tIS and tDS) nominal slew rate for a rising signal is defined as the slew rate between the last crossing of VRef and the first crossing of

VIH(AC)min. Setup (tIS and tDS) nominal slew rate for a falling signal is defined as the slew rate between the last crossing of VRef and the first crossing

of VIL(AC)max.

8.5.2 Input Slew Rate for Input Hold Time (tIH) and Data Hold Time (tDH)

Hold nominal slew rate for a rising signal is defined as the slew rate between the last crossing of VIL(DC)max and the first crossing of VRef. Hold (tIH &

tDH) nominal slew rate for a falling signal is defined as the slew rate between the last crossing of VIH(DC)min and the first crossing of VRef

[ Table 12 ] Single Ended Input Slew Rate definition

Notes: This nominal slew rate applies for linear signal waveforms.

Description

Measured

From

Defined by

Applicable for

To

Input slew rate for rising edge

Vref

Vih(AC)min

Vih(AC)min-Vref

Delta TRS

Vref-Vil(AC)max

Delta TFS

Vref-Vil(DC)max

Delta TFH

Vih(DC)min-Vref

Delta TRH

Setup

(tIS,tDS)

Input slew rate for falling edge

Vref

Vil(AC)max

Input slew rate for rising edge

Vil(DC)max

Vref

Hold

(tIH,tDH)

Input slew rate for falling edge

Vih(DC)min

Vref

V

DDQ

V

IH(ac)

min

V

IH(dc)

min

V

REF

V

IL(dc)

max

V

IL(ac)

max

V

SSQ

< Figure : Input slew rate for setup>

V

SWING(MAX)

delta TRS

delta TFS

V

DDQ

V

IH(ac)

min

V

IH(dc)

min

V

REF

V

IL(dc)

max

V

IL(ac)

max

V

SSQ

V

SWING(MAX)

delta TRH

delta TFH

< Figure : Input slew rate for Hold>

[ Table 13 ] Differential input slew rate definition

Note : The differential signal (i.e. CK - CK and DQS - DQS) must be linear between these thresholds

Description

Measured

From

Defined by

To

Differential input slew rate for rising edge (CK-

CK and DQS-DQS)

VILdiffmax

VIHdiffmin

VIHdiffmin - VILdiffmax

Delta TRdiff

VIHdiffmin - VILdiffmax

Delta TFdiff

Differential input slew rate for falling edge (CK-

CK and DQS-DQS)

VIHdiffmin

VILdiffmax

VDDQ

VIHdiffmin

V

REF

VILdiffmax

VSSQ

V

SWING(MAX)

delta TRdiff

delta TFdiff

8.5 Slew rate definition for Single Ended Input Signals

8.6 Slew rate definition for Differential Input Signals

Figure 5. Input Nominal Slew Rate definition for Singel ended Signals

Figure 6. Differential Input Slew Rate definition for DQS, DQS and CK, CK

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K4B1G1646C-ZCG9 | 1Gb C-die DDR3 SDRAM Specification |

| K4C560838C-TCD3 | 256Mb Network-DRAM |

| K4C560838C-TCD4 | Aluminum Electrolytic Radial Lead High Ripple, Long Life Capacitor; Capacitance: 150uF; Voltage: 200V; Case Size: 16x31.5 mm; Packaging: Bulk |

| K4C560838C-TCDA | Aluminum Electrolytic Radial Lead High Ripple, Long Life Capacitor; Capacitance: 220uF; Voltage: 200V; Case Size: 18x31 mm; Packaging: Bulk |

| K4C561638C-TCD3 | 256Mb Network-DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K4B1G1646C-ZCG9 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:1Gb C-die DDR3 SDRAM Specification |

| K4B1G1646D | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:1Gb D-die DDR3 SDRAM Specification |

| K4B1G1646D-HCF7 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:1Gb D-die DDR3 SDRAM Specification |

| K4B1G1646D-HCF8 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:1Gb D-die DDR3 SDRAM Specification |

| K4B1G1646D-HCH9 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:1Gb D-die DDR3 SDRAM Specification |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。