- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄384402 > HF88M08 (King Billion Electronics Co., Ltd.) 512K x 8 bit Mask ROM PDF資料下載

參數(shù)資料

| 型號(hào): | HF88M08 |

| 廠商: | King Billion Electronics Co., Ltd. |

| 英文描述: | 512K x 8 bit Mask ROM |

| 中文描述: | 為512k × 8位掩模ROM |

| 文件頁(yè)數(shù): | 8/19頁(yè) |

| 文件大小: | 320K |

| 代理商: | HF88M08 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)

King Billion Electronics Co., Ltd

駿 億 電 子 股 份 有 限 公 司

HF88M08

unnecessary power drain.

January 16, 2004

This specification is subject to change without notice. Please contact sales person for the latest version before use.

Page 8 of 19

V1.11

RS

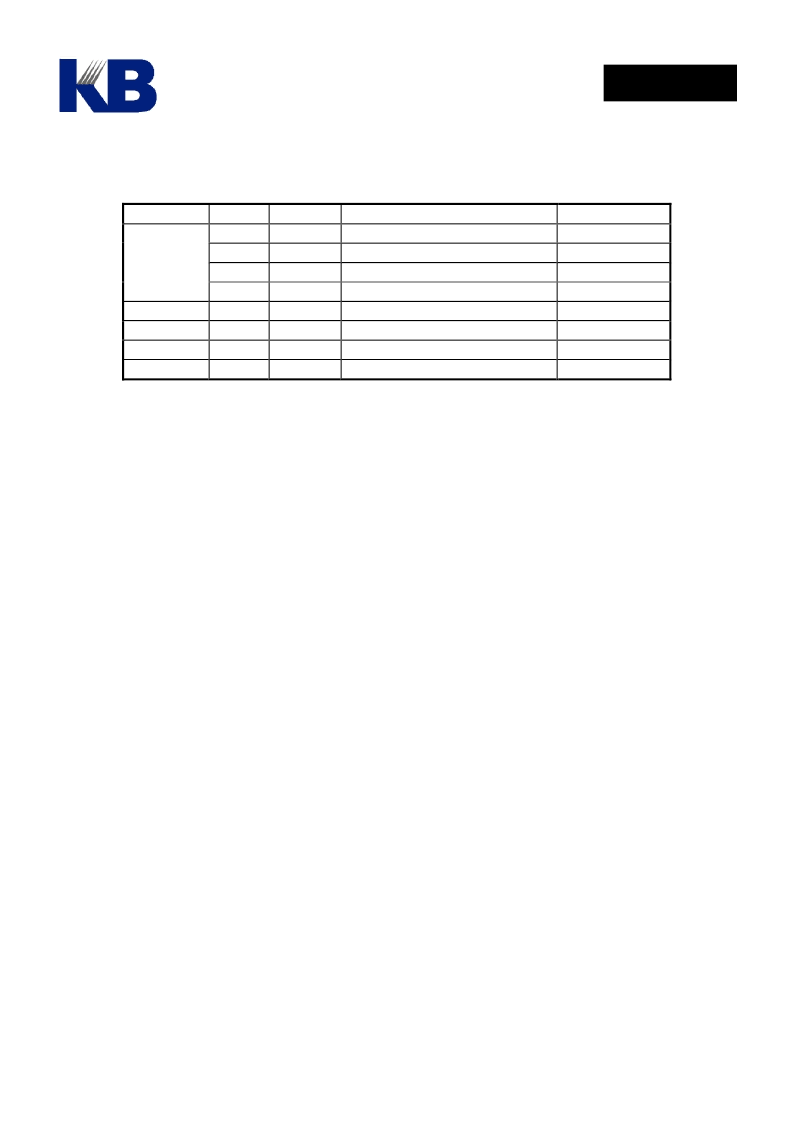

2

RS

1

RS

0

Symbol

0xx

Type

R

W

W

W

R/W

R/W

R/W

R/W

Description

Read data by Indirect access

Address latch 2 for A19 ~ A16

Address latch 1 for A15 ~ A8

Address latch 0 for A7 ~ A0

Port 0 Output Register

Direction Register 0

Port 1 Output Register

Direction Register 0

Initial Value

“--------“

“--------“

“--------“

“11111111“

“00000000“

“11111111“

“00000000“

AC2

AC1

AC0

P0

DIR0

P1

DIR1

100

101

110

111

6.1

Retrieve data in Data File

Accesses to the ROM contents, expansion I/O, Address Counter and Direction registers are made through

8 Data I/O pins – D7 ~ D0. With Register Selection RS = “0xx”, the starting addresses can be written

through Data I/Os by bringing WEn to low and back to high. Addresses are latched on the rising edge of

WEn.

Once the starting address of data block is latched into the Address Counter, data may be read out by

sequentially pulsing OEn with CEn staying low. When at ‘0’, the OEn gate the data of the selected

address unto Data I/O pin D7 ~ D0. With the rising edge of OEn, the internal Address Counter is

incremented by one automatically.

6.2

Loading the Address Counter

Before the data can be retrieved, the Address Counter must be initialized with the starting address, then

the contents of ROM pointed to by Address Counter (AC) can be accessed through D7 through D0. In

order to simplify the procedure of loading 20-bit Address Counter (AC), a internal pointer is implemented

and used to point to next register to write in the up to three-cycle address loading sequence. Initially,

with RS = “0xx” CEn goes from ‘1’ to ‘0’ and the AC pointer is initialized. The pointer is then

incremented to point to next register with falling edge of each WEn pulse. So when randomly accessing

data within a 256-byte page, or within a 64K-byte block mode, then only one or two-cycle address reload

process is needed to access different locations within a page or block.

The Address Counter pointer will be held in reset state in the following conditions:

1.

When CEn is '1' (the device is deselected).

2.

By the Read pulse (OEn is '0') and RS2 = '0' (ROM is being accesses).

The inclusion of the 3rd condition is to force the address loading to start from LSB of Address Counter

once the read cycle is initiated. However, the AC Pointer will not be reset when reading or writing

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HF88M32B | command interfaced 4M x 8 bit Mask ROM |

| HF88S05 | command mode SRAM device |

| HFA1105 | 144 MACROCELL 5 VOLT ISP CPLD - NOT RECOMMENDED for NEW DESIGN |

| HFA1105IP | 330MHz, Low Power, Current Feedback Video Operational Amplifier |

| HFA1105IB | Circular Connector; MIL SPEC:MIL-C-26482, Series I, Solder; Body Material:Aluminum; Series:PT06; No. of Contacts:41; Connector Shell Size:22; Connecting Termination:Solder; Circular Shell Style:Straight Plug; Body Style:Straight |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HF88M08(S) | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述: |

| HF88M32(S) | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述: |

| HF88M32B | 制造商:KB 制造商全稱(chēng):KB 功能描述:command interfaced 4M x 8 bit Mask ROM |

| HF88M32B(S) | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述: |

| HF88S05 | 制造商:KB 制造商全稱(chēng):KB 功能描述:command mode SRAM device |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。