- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384400 > HEF4046BP (NXP Semiconductors N.V.) Phase-locked loop PDF資料下載

參數(shù)資料

| 型號: | HEF4046BP |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類: | 通用總線功能 |

| 英文描述: | Phase-locked loop |

| 封裝: | HEF4046BP<SOT38-4 (DIP16)|<<http://www.nxp.com/packages/SOT38-4.html<1<Always Pb-free,;HEF4046BT<SOT109-1 (SO16)|<<http://www.nxp.com/packages/SOT109-1.html<1<week |

| 文件頁數(shù): | 3/19頁 |

| 文件大小: | 178K |

| 代理商: | HEF4046BP |

HEF4046B_4

NXP B.V. 2010. All rights reserved.

Product data sheet

Rev. 04 — 5 January 2010

3 of 19

NXP Semiconductors

HEF4046B

Phase-locked loop

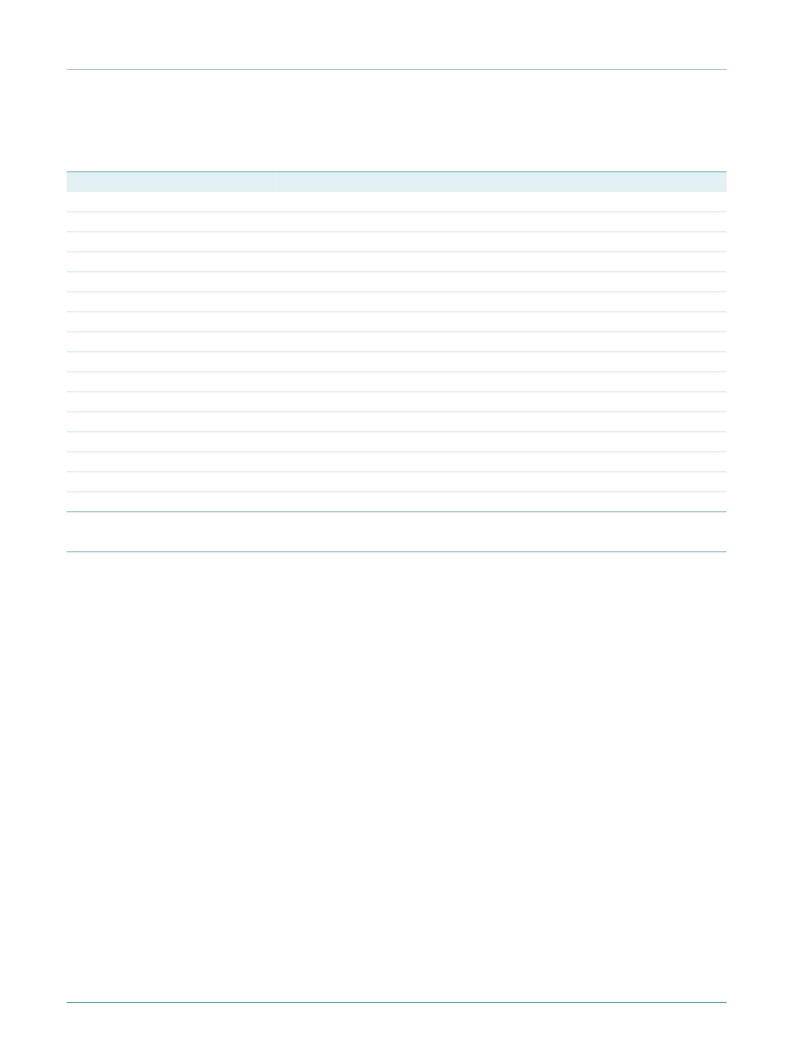

6.2 Pin description

7.

Functional description

7.1 VCO control

The VCO requires an external capacitor (C1) and resistor (R1) with an optional resistor

(R2). Resistor R1 and capacitor C1 determine the frequency range of the VCO, while

resistor R2 enables the VCO to have a frequency off-set if required. The high input

impedance of the VCO simplifies the design of low-pass filters; it permits the designer a

wide choice of resistor/capacitor ranges. In order not to load the low-pass filter, a

source-follower output of the VCO input voltage is provided at SF_OUT (pin 10). If this is

used, a load resistor (R

L

) should be connected from SF_OUT to V

SS

; if unused, SF_OUT

should be left open. The VCO output (pin 4) can either be connected directly to the

comparator input COMP_IN (pin 3) or via a frequency divider. A LOW-level at the inhibit

input INH_IN (pin 5) enables the VCO and the source follower, while a HIGH-level turns

both off to minimize standby power consumption.

7.2 Phase comparators

The phase-comparator signal input SIG_IN (pin 14) can be direct-coupled, provided the

signal swing is between the standard HE4000B family input logic levels. The signal must

be capacitively coupled to the self-biasing amplifier at the signal input with smaller swings.

Phase comparator 1 is an EXCLUSIVE-OR network. The signal and comparator input

frequencies must have a 50 % duty factor to obtain the maximum lock range. The average

output voltage of the phase comparator is equal to 0.5V

DD

when there is no signal or noise

at the signal input. The average voltage to the VCO input VCO_IN is supplied by the

low-pass filter connected to the output of phase comparator 1. This also causes the VCO

to oscillate at the center frequency (f

0

). The frequency capture range (2f

C

) is defined as

Table 2.

Symbol

PCP_OUT

PC1_OUT

COMP_IN

VCO_OUT

INH

C1A

C1B

V

SS

VCO_IN

SF_OUT

R1

R2

PC2_OUT

SIG_IN

ZENER

V

DD

Pin description

Pin

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

Description

phase comparator pulse output

phase comparator 1 output

comparator input

VCO output

inhibit input

capacitor C1 connection A

capacitor C1 connection B

ground supply voltage

VCO input

source-follower output

resistor R1 connection

resistor R2 connection

phase comparator 2 output

signal input

Zener diode input for regulated supply

supply voltage

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HEF4046BT | Phase-locked loop |

| HEF4047BP | Monostable-astable multivibrator |

| HEF4047BT | Monostable-astable multivibrator |

| HEF4049BP | Hex inverting buffers |

| HEF4049BT | Hex inverting buffers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HEF4046BP,652 | 功能描述:鎖相環(huán) - PLL PHASE LOCKED LOOP W/VCO RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| HEF4046BP652 | 制造商:NXP Semiconductors 功能描述:IC PHASE LOCKED LOOP (PLL) VCO 2.7MHZ |

| HEF4046BPN | 制造商:NXP Semiconductors 功能描述:PLL Single 16-Pin PDIP Bulk |

| HEF4046BT | 制造商:NXP Semiconductors 功能描述:IC 4000 LOCMOS SMD 4046 SOIC16 制造商:NXP Semiconductors 功能描述:IC, 4000 LOCMOS, SMD, 4046, SOIC16 制造商:NXP Semiconductors 功能描述:IC, 4000 LOCMOS, SMD, 4046, SOIC16; PLL Type:VCO; Frequency:7MHz; Supply Current:750A; Supply Voltage Min:3V; Supply Voltage Max:15V; Digital IC Case Style:SOIC; No. of Pins:16; Operating Temperature Min:-40C; Operating Temperature;RoHS Compliant: Yes |

| HEF4046BT,652 | 功能描述:鎖相環(huán) - PLL PHASE LOCKED LOOP RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。