- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄384296 > EM78568 (Electronic Theatre Controls, Inc.) 8-BIT MICRO-CONTROLLER for FRS PDF資料下載

參數(shù)資料

| 型號(hào): | EM78568 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 8-BIT MICRO-CONTROLLER for FRS |

| 中文描述: | 8位微控制器為FRS |

| 文件頁(yè)數(shù): | 15/54頁(yè) |

| 文件大小: | 494K |

| 代理商: | EM78568 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)當(dāng)前第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)

EM78568

8-bit Micro-controller for FRS

__________________________________________________________________________________________________________________________________________________________________

* This specification are subject to be changed without notice.

07/28/2004 V3.5

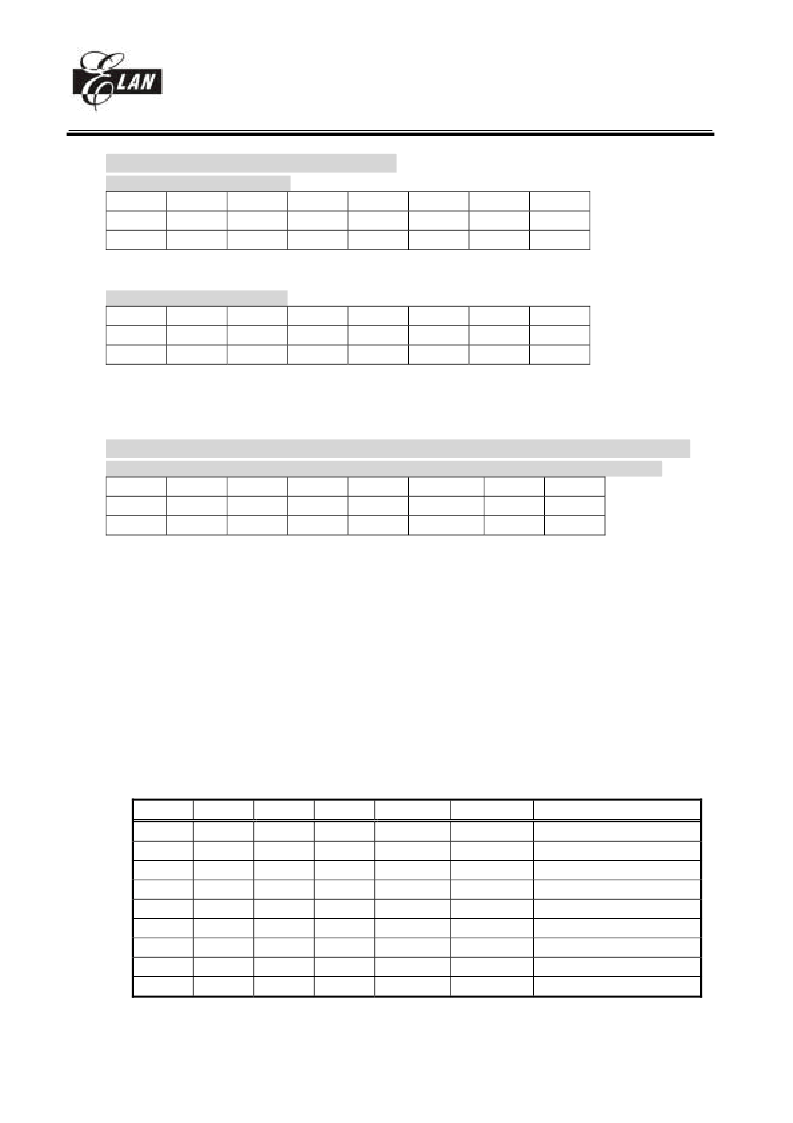

R9 (PORT9 I/O data, Data RAM data buffer)

PAGE0 (PORT9 I/O data register)

7

6

P97

P96

P95

R/W

R/W

R/W

Bit 0 ~ Bit 7 (P90 ~ P97) : 8-bit PORT9(0~7) I/O data register

User can use IOC register to define input or output each bit.

PAGE1 (Data RAM data register)

7

6

5

RAM_D7 RAM_D6 RAM_D5 RAM_D4 RAM_D3 RAM_D2 RAM_D1 RAM_D0

R/W

R/W

R/W

R/W

Bit 0 ~ Bit 7 (RAM_D0 ~ RAM_D7) : Data RAM’s data

The address for data RAM is accessed from R8 PAGE1. The data RAM bank is selected by R7 PAGE1 Bit

0 ~ Bit 1 (RAM_B0 ~ RAM_B1).

RA (PLL, Main clock selection, Comparator flag, Watchdog timer, DAC input data buffer)

PAGE0 (PLL enable bit, Main clock selection bits, Comparator control bits, Watchdog timer enable bit)

7

6

5

4

3

IDLE

PLLEN

CLK2

CLK1

CLK0

R/W-0

R/W-0

R/W-0

R/W-1

R/W-1

Bit 0(WDTEN) : Watch dog control bit

User can use WDTC instruction to clear watch dog counter. The counter 's clock source is 32768/2 Hz. If

the prescaler assigns to TCC. Watch dog will time out by (1/32768 )*2 * 256 = 15.616mS. If the

prescaler assigns to WDT, the time of time out will be more times depending on the ratio of prescaler.

0/1

disable/enable

Bit 1(CMPREF) : Comparator’s reference voltage source selection bit

0

Comparator’s reference voltage is driven from internal bias resistor string. This reference voltage level

can be set by RD PAGE0 bit 0 ~ bit 5 (CMP_B0 ~ CMP_B5).

1

Comparator’s reference voltage is driven from external bias. This reference voltage input is CMP3/P65

pin. Also IOC6 PAGE1 bit 2(CMP63/P63) should be set to “1”.

Bit 2(CMPFLAG) : Output of the comparator

0

Input voltage < reference voltage

1

input voltage > reference voltage

Bit 3 ~ Bit 5 (CLK0 ~ CLK2) : MAIN clock selection bits

User can choose different frequency of main clock by CLK1 and CLK2. All the clock selection is list below.

PLLEN

CLK2

CLK1

CLK0

Sub clock

1

0

0

0

32.768kHz

1

0

0

1

32.768kHz

1

0

1

0

32.768kHz

1

0

1

1

32.768kHz

1

1

0

0

32.768kHz

1

1

0

1

32.768kHz

1

1

1

0

32.768kHz

1

1

1

1

32.768kHz

0

don’t care

don’t care

32.768kHz

5

4

3

2

1

0

P94

R/W

P93

R/W

P92

R/W

P91

R/W

P90

R/W

4

3

2

1

0

R/W

R/W

R/W

R/W

2

1

0

CMPFLAG CMPREF WDTEN

R

R/W-0

R/W-0

MAIN clock

447.829kHz

895.658kHz

1.791MHz

3.582MHz

7.165MHz

10.747MHz

14.331MHz

17.913MHz

don’t care

CPU clock

447.829kHz (Normal mode)

895.658kHz (Normal mode)

1.791MHz (Normal mode)

3.582MHz (Normal mode)

7.165MHz (Normal mode)

10.747MHz (Normal mode)

14.331MHz (Normal mode)

17.913MHz (Normal mode)

32.768kHz (Green mode)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EMA2 | Emitter common (dual digital transistors) |

| EMA3 | Emitter common (dual digital transistors) |

| EMA4 | General purpose (dual digital transistors) |

| EMB4 | General purpose (dual digital transistors) |

| EMA5 | Emitter common (dual digital transistors) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EM78569 | 制造商:EMC 制造商全稱:ELAN Microelectronics Corp 功能描述:8-BIT MICRO-CONTROLLER |

| EM785830AA | 制造商:EMC 制造商全稱:ELAN Microelectronics Corp 功能描述:8-BIT MICRO-CONTROLLER |

| EM785830AAM | 制造商:EMC 制造商全稱:ELAN Microelectronics Corp 功能描述:8-BIT MICRO-CONTROLLER |

| EM785830AAP | 制造商:EMC 制造商全稱:ELAN Microelectronics Corp 功能描述:8-BIT MICRO-CONTROLLER |

| EM785830AD | 制造商:EMC 制造商全稱:ELAN Microelectronics Corp 功能描述:8-BIT MICRO-CONTROLLER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。