- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄379059 > CY7C1304V25 (Cypress Semiconductor Corp.) 9-Mb Pipelined SRAM with QDR Architecture(帶QDR結(jié)構(gòu)的9-M位流水線式 SRAM) PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C1304V25 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | 9-Mb Pipelined SRAM with QDR Architecture(帶QDR結(jié)構(gòu)的9-M位流水線式 SRAM) |

| 中文描述: | 9 - MB的流水線架構(gòu)的SRAM與國(guó)防評(píng)估報(bào)告(帶國(guó)防評(píng)估報(bào)告結(jié)構(gòu)的9米位流水線式的SRAM) |

| 文件頁(yè)數(shù): | 15/23頁(yè) |

| 文件大小: | 216K |

| 代理商: | CY7C1304V25 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)當(dāng)前第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)

CY7C1304V25

Advanced Information

15

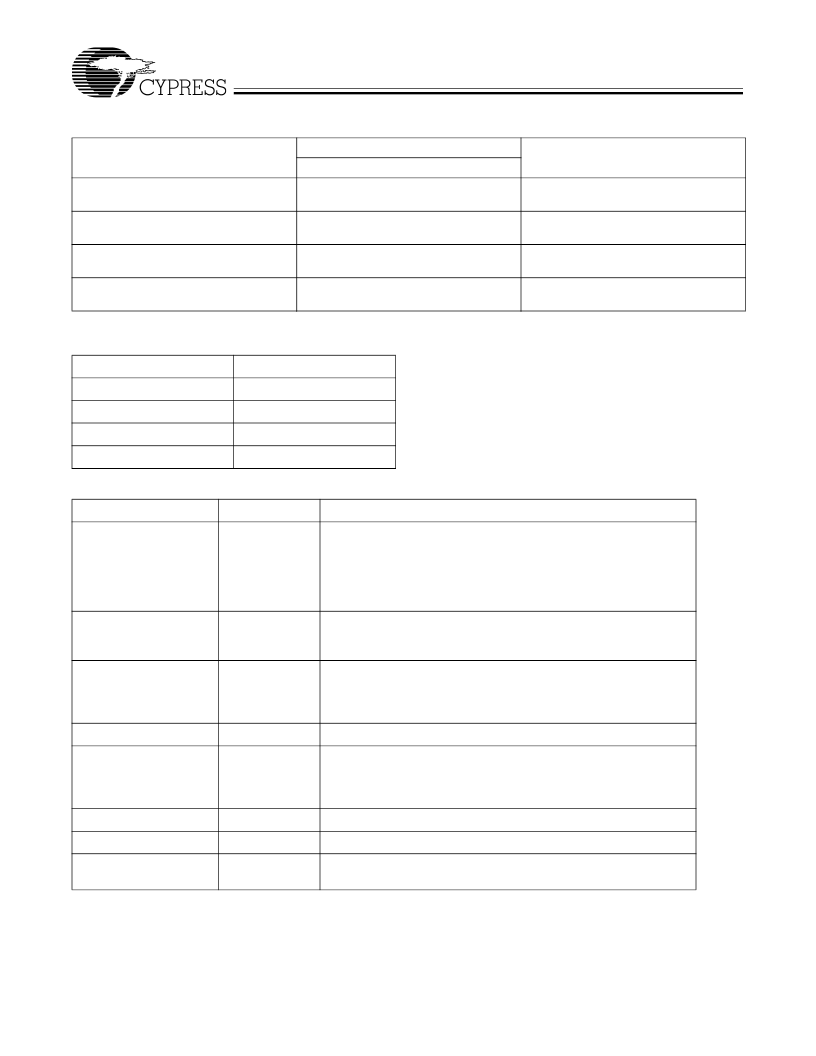

Identification Register Definitions

Instruction Field

Value

Description

CY7C1304V25

Revision Number

(31:29)

000

Version number.

Cypress Device ID

(28:12)

01011010011010110

Defines the type of SRAM.

Cypress JEDEC ID

(11:1)

00000110100

Allows unique identification of SRAM

vendor.

ID Register Presence

(0)

1

Indicate the presence of an ID register.

Scan Register Sizes

Register Name

Bit Size

Instruction

3

Bypass

1

ID

32

Boundary Scan

69

Instruction Codes

Instruction

Code

Description

EXTEST

000

Captures the Input/Output ring contents. Places the boundary scan

register between the TDI and TDO. This instruction is not 1149.1 com-

pliant.

The EXTEST command implemented by the CY7C1304V25

device will NOT place the output buffers into a HIGH-Z condition.

If the output buffers need to be HIGH-Z condition, this can be

accomplished by deselecting the Read port.

IDCODE

001

Loads the ID register with the vendor ID code and places the register

between TDI and TDO. This operation does not affect SRAM opera-

tion.

SAMPLE Z

010

Captures the Input/Output contents. Places the boundary scan register

between TDI and TDO.

The SAMPLE Z command implemented by

the CY7C1304V25 device will place the output buffers into a

HIGH-Z condition.

RESERVED

011

Do Not Use: This instruction is reserved for future use.

SAMPLE/PRELOAD

100

Captures the Input/Output ring contents. Places the boundary scan

register between TDI and TDO. Does not affect the SRAM operation.

This instruction does not implement 1149.1 preload function and is

therefore not 1149.1 compliant.

RESERVED

101

Do Not Use: This instruction is reserved for future use.

RESERVED

110

Do Not Use: This instruction is reserved for future use.

BYPASS

111

Places the bypass register between TDI and TDO. This operation does

not affect SRAM operation.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C1305BV25-100BZC | 18-Mbit Burst of 4 Pipelined SRAM with QDR Architecture |

| CY7C1307BV25 | 18-Mbit Burst of 4 Pipelined SRAM with QDR Architecture |

| CY7C1307BV25-100BZC | 18-Mbit Burst of 4 Pipelined SRAM with QDR Architecture |

| CY7C1307BV25-133BZC | 18-Mbit Burst of 4 Pipelined SRAM with QDR Architecture |

| CY7C1307BV25-167BZC | 18-Mbit Burst of 4 Pipelined SRAM with QDR Architecture |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1304V25-200BZC | 制造商:Cypress Semiconductor 功能描述:9MB PIPELINE QDR SRAM 2.5V CORE, FBGA - Trays |

| CY7C1305 WAF | 制造商:Cypress Semiconductor 功能描述: |

| CY7C13055DC | 制造商:CYPRESS 功能描述:* |

| CY7C130-55PC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 1K x 8 Dual-Port 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1305BV25-167BZC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 1Mx18 2.5V QDR 靜態(tài)隨機(jī)存取存儲(chǔ)器 COM RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。